Research

Machine Learning and GNNs for EDA

Our lab is at the forefront of applying machine learning and graph neural networks (GNNs) to electronic design automation challenges. We develop modern AI techniques to create faster and more efficient design tools for next-generation chips.

- GATMesh: We use graph neural networks for clock mesh timing analysis to significantly improve both accuracy and efficiency compared to traditional methods.

- GAT-Steiner: We apply GNNs to predict optimal Rectilinear Steiner Minimal Trees, optimizing interconnect routing in physical design.

- Effective Capacitance Modeling: We leverage GNNs to model complex capacitance effects in modern chip designs, providing more precise timing and power analysis.

Related papers:

- M. H. Khan, M. Guthaus, “GATMesh: Clock Mesh Timing Analysis using Graph Neural Networks,” arXiv preprint arXiv:2507.05681, 2025.

- E. Dogan, M. R. Guthaus, “Effective Capacitance Modeling Using Graph Neural Networks,” 27th International Symposium on Quality Electronic Design (ISQED), 2026.

- B. Onal, E. Dogan, M. H. Khan, M. R. Guthaus, “GAT-Steiner: Rectilinear Steiner Minimal Tree Prediction Using GNNs,” Proceedings of the 43rd IEEE/ACM International Conference on Computer-Aided Design (ICCAD), 2024.

Open-Source Memory Compilers

Our lab focuses on the development of open-source compilers to automate the design and generation of high-performance memory architectures.

OpenRAM

The OpenRAM project aims to provide a free, open-source memory compiler development framework for Random-Access Memories (RAMs). It is a joint development project between University of California Santa Cruz and Oklahoma State University to enable memory and computer system research by creating an open-source compiler infrastructure.

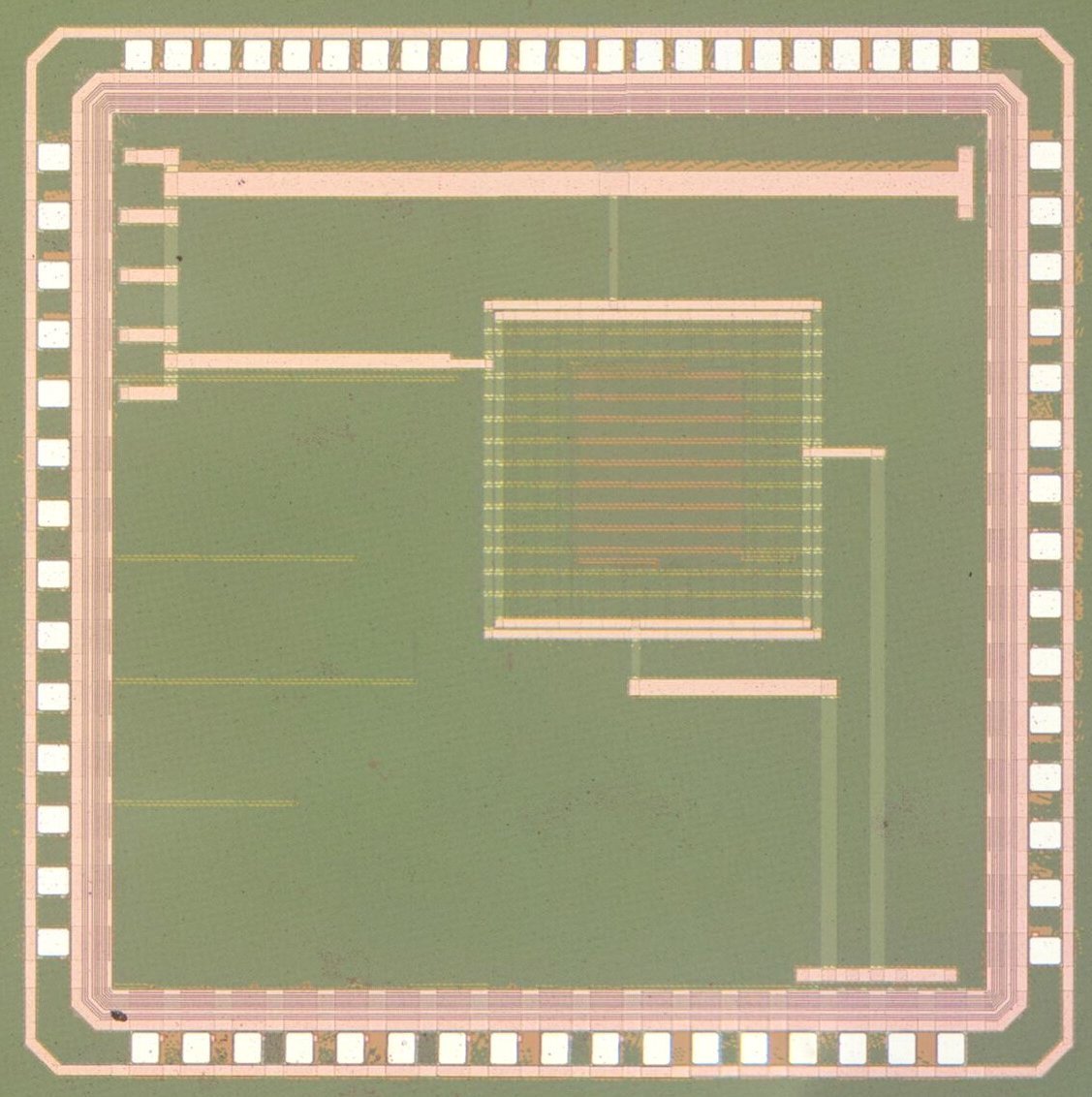

First OpenRAM Silicon in Skywater 130nm

OpenGCRAM

The OpenGCRAM project provides an open-source gain cell compiler that enables design-space exploration optimized for AI workloads. It offers a flexible framework for investigating novel memory bitcells and architectures beyond traditional SRAM.

Related papers:

- X. Wang et al., “OpenGCRAM: An Open-Source Gain Cell Compiler Enabling Design-Space Exploration for AI Workloads,” arXiv preprint arXiv:2507.10849, 2025.

- M. R. Guthaus, J. E. Stine, S. Ataei, B. Chen, B. Wu, M. Sarwar, “OpenRAM: An Open-Source Memory Compiler,” Proceedings of the 35th International Conference on Computer-Aided Design (ICCAD), 2016

- S. Ataei, J. Stine, M. Guthaus, “A 64 kb differential single-port 12T SRAM design with a bit-interleaving scheme for low-voltage operation in 32 nm SOI CMOS,” International Conference on Computer Design (ICCD), 2016, pp. 499-506.

- E. Ebrahimi, M. Guthaus, J. Renau, “Timing Speculative SRAM”, IEEE In- ternational Symposium on Circuits and Systems (ISCAS), 2017

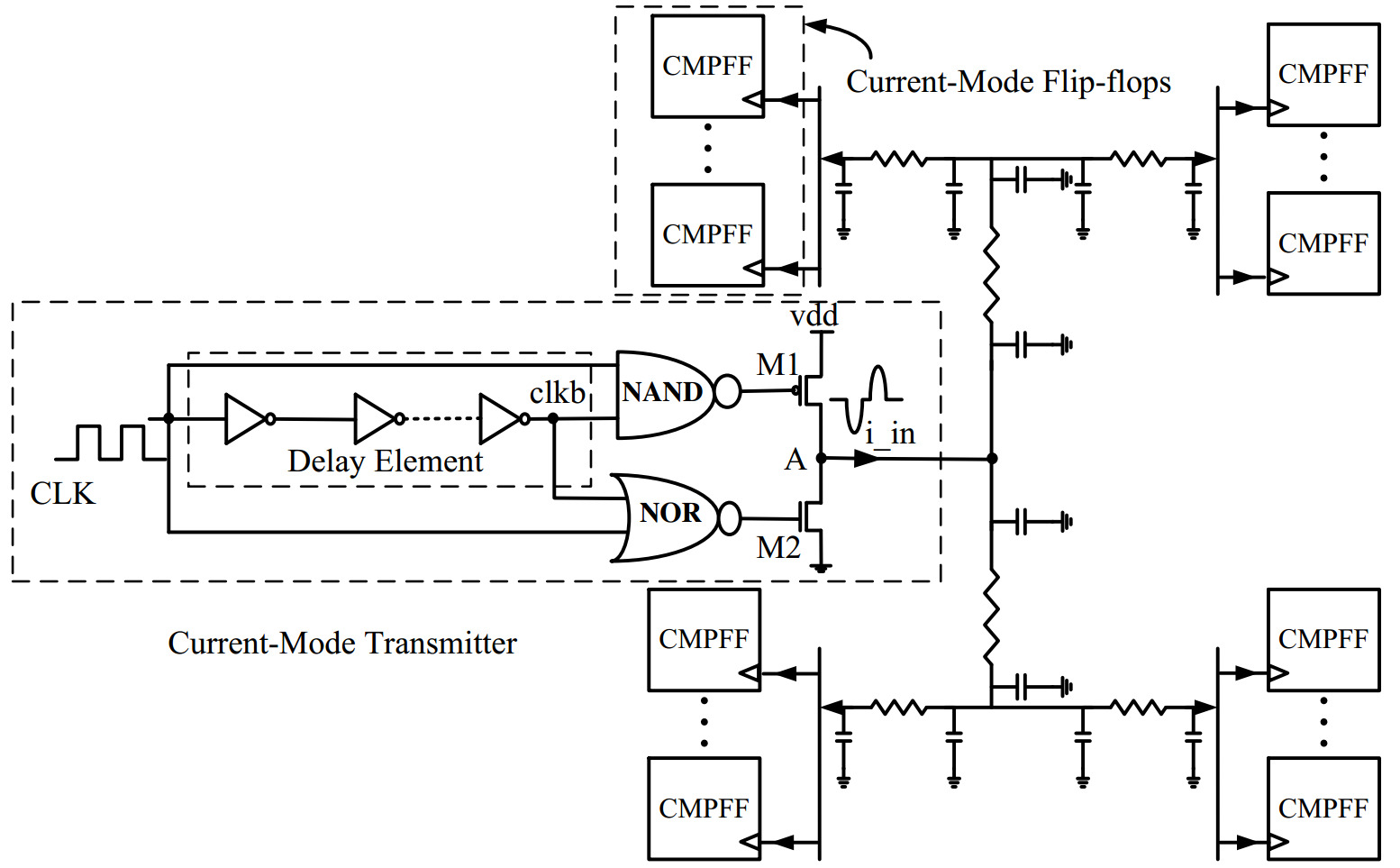

Current-Mode Clocking

In a high-performance computer system design, the clock network consumes a significant amount of power and causes the most switching noise. High power consumption requires larger batteries while switching noise degrades the accuracy of sensitive sensor measurements in modern Systems-on-Chips. Prof. Matthew Guthaus, faculty in Computer Engineering, and his graduate student Riadul Islam, now a faculty at University of Michigan Dearborn, have developed the concept of a current-mode clock distribution to address these problems. Current-mode clocking senses current flow rather than a traditional voltage swing in clock wires and thereby eliminates most of the noise and power problems in traditional clock distribution schemes. Current-mode clocking simultaneously increases the potential maximum speeds of computer chips for performance improvements.

Current-Mode Clock Distribution

Related papers:

- R. Islam, M. R. Guthaus, “HCDN: Hybrid-Mode Clock Distribution Networks”, IEEE Transactions on Circuits and Systems I: Regular Papers, 2018.

- R. Islam, H. Fahmy, P. Lin, M. R. Guthaus, “DCMCS: Highly Robust Low-Power Differential Current-Mode Clocking and Synthesis”, IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2018.

- R. Islam, M. R. Guthaus, “Current-Mode Clock Distribution,” IEEE Inter- national Symposium on Circuits and Systems (ISCAS), 2014, pp. 1203-1206.

- R. Islam, H. Fahmy, P.-Y. Lin, M. R. Guthaus, “Differential Current-Mode Clock Distribution,” Midwest Symposium on Circuits and Systems (MWSCAS), 2015, pp. 1-4.

- R. Islam, M. R. Guthaus, “Low-Power Clock Distribution Using a Current- Pulsed Clocked Flip-Flop,” IEEE Transactions on Circuits and Systems I (TCAS-I), Volume 62, Issue 4, April 2015, pp. 1156-1164.

- R. Islam, M. R. Guthaus, “CMCS: Current-Mode Clock Synthesis,” IEEE Transactions on VLSI (TVLSI), Volume 25, Issue 3, September 2016, pp. 1054-1062.

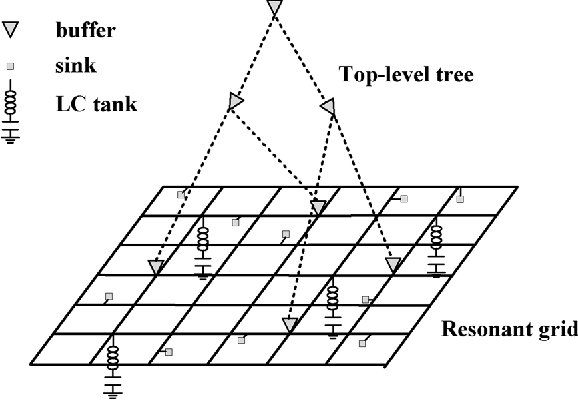

Resonant and Charge-Recovery Clocking

Distributed-LC Resonant Clocking

- H. Fahmy, P.-Y. Lin, R. Islam, M. R. Guthaus, “Switched Capacitor Quasi- Adiabatic Clocks,” IEEE International Symposium on Circuits and Systems (ISCAS), 2015, pp. 1398-1401.

- P.-Y.Lin,H.Fahmy,R.Islam,M.R.Guthaus,“LC Resonant Clock Resource Minimization using Compensation Capacitance,” IEEE International Symposium on Circuits and Systems (ISCAS), 2015, pp. 1406-1409.

- B. Lacara, P.-Y. Lin, M. R. Guthaus, “Multi-Frequency Resonant Clocks,” IEEE International Symposium on Circuits and Systems (ISCAS), 2015, pp. 1402- 1405.

- X. Hu, M. R. Guthaus, “Distributed LC Resonant Clock Grid Synthesis,” IEEE Transactions on Circuits and Systems I (TCAS-I), Volume 59, Number 11, November 2012, pp. 2749-2760.

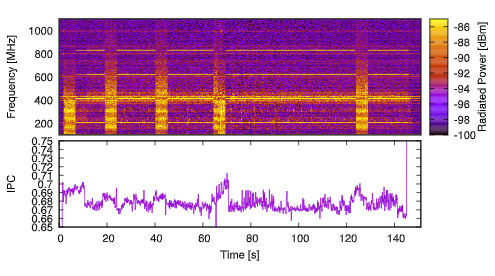

Electromagnetic Interference

EMI Patterns on sjeng benchmark

- D. Gorman, M. R. Guthaus, J. Renau, “Architectural opportunities for novel dynamic EMI shifting (DEMIS)”, IEEE/ACM International Symposium on Microarchitecture, 2017.

- X. Hu, M.R. Guthaus, “Clock tree optimization for electromagnetic compatibility (EMC)”, Asia and South Pacific Design Automation Conference, 2011.