HighTide

A diverse, actively maintained open-source VLSI benchmark suite spanning multiple design languages and technology nodes, built on the OpenROAD RTL-to-GDSII flow.

A diverse, actively maintained open-source VLSI benchmark suite spanning multiple design languages and technology nodes, built on the OpenROAD RTL-to-GDSII flow.

Existing benchmarks haven't kept pace with modern hardware diversity.

Evaluation of EDA tools, circuits, and systems often relies on outdated hardware benchmarks. Existing benchmark designs are predominantly RISC-V CPUs, providing limited representation of the diverse components found in modern heterogeneous SoCs—from ML accelerators and GPUs to cryptographic engines and networking cores.

The growing diversity of design languages poses an additional challenge. While designs exploiting the parameterization capabilities of Chisel, Python-based generators, and SystemVerilog are increasingly prevalent in the open-source community, the majority of benchmarks available to suites remain Verilog-only snapshots—often never updated after their initial release.

For designs actively receiving upstream updates, relying on stale static snapshots risks producing results that no longer reflect a design's true complexity and structure. Models trained on a narrow design set learn patterns specific to those designs, rather than generalizable circuit behaviors. HighTide addresses these gaps with a benchmark suite that evolves alongside the open-source hardware ecosystem.

Processors, accelerators, cryptographic engines, and networking cores—not just CPUs. Cell counts range from under 20k to over 1M.

Designs originating from Verilog, SystemVerilog, Chisel, Python (LiteX), and migen, compiled down to Verilog for physical implementation.

Git submodules track upstream sources. Updates are summarized and applied with AI-assisted Claude Code skills.

End-to-end RTL-to-GDSII benchmarks exercising synthesis, floorplanning, placement, CTS, routing, and sign-off—not just point-tool targets.

Infrastructure designed for reproducibility, scalability, and continuous evolution.

Targets ASAP7 (7nm), NanGate45 (45nm), and SKY130HD (130nm) technology nodes, enabling cross-node design exploration and tool evaluation.

Leverages OpenROAD-flow-scripts and the OpenROAD toolchain for an open, reproducible RTL-to-GDSII flow. Designs run within a Docker image by default, eliminating manual tool installation.

Bazel-ORFS integration partitions the flow into separate build targets, enabling incremental re-execution and remote caching to drastically reduce runtimes for large designs.

Tagged Git releases provide stable, versioned snapshots while regularly incorporating upstream changes through Git submodules for reproducible evaluation.

Diverse designs with varying structural composition—sequential-heavy, combinational-heavy, macro-dense—provide rich training data for ML-driven EDA research.

Fully open-source and designed to grow. Contribute new designs, improve existing configurations, or use the suite for your research.

Hardware blocks typically found in commercial heterogeneous SoCs.

| Design | Description | Language | Platforms |

|---|---|---|---|

| BlackParrot | RISC-V multicore processor (single & quad core) | SystemVerilog | asap7 |

| Gemmini | Systolic array matrix multiplication accelerator | Chisel | asap7 |

| SHA3 | SHA-3 cryptographic hash accelerator | Chisel | asap7 |

| CNN | Convolutional neural network accelerator | Verilog | asap7 |

| NyuziProcessor | GPGPU-style multicore vector processor | SystemVerilog | asap7 nangate45 |

| Minimax | Minimal area RISC-V core (serially-fetched) | Verilog | asap7 nangate45 sky130hd |

| LFSR | LFSR-based pseudo-random bit sequence generator | Verilog | asap7 nangate45 sky130hd |

| LiteEth | Lightweight Ethernet core (6 MAC/PHY variants) | Migen/LiteX | asap7 nangate45 sky130hd |

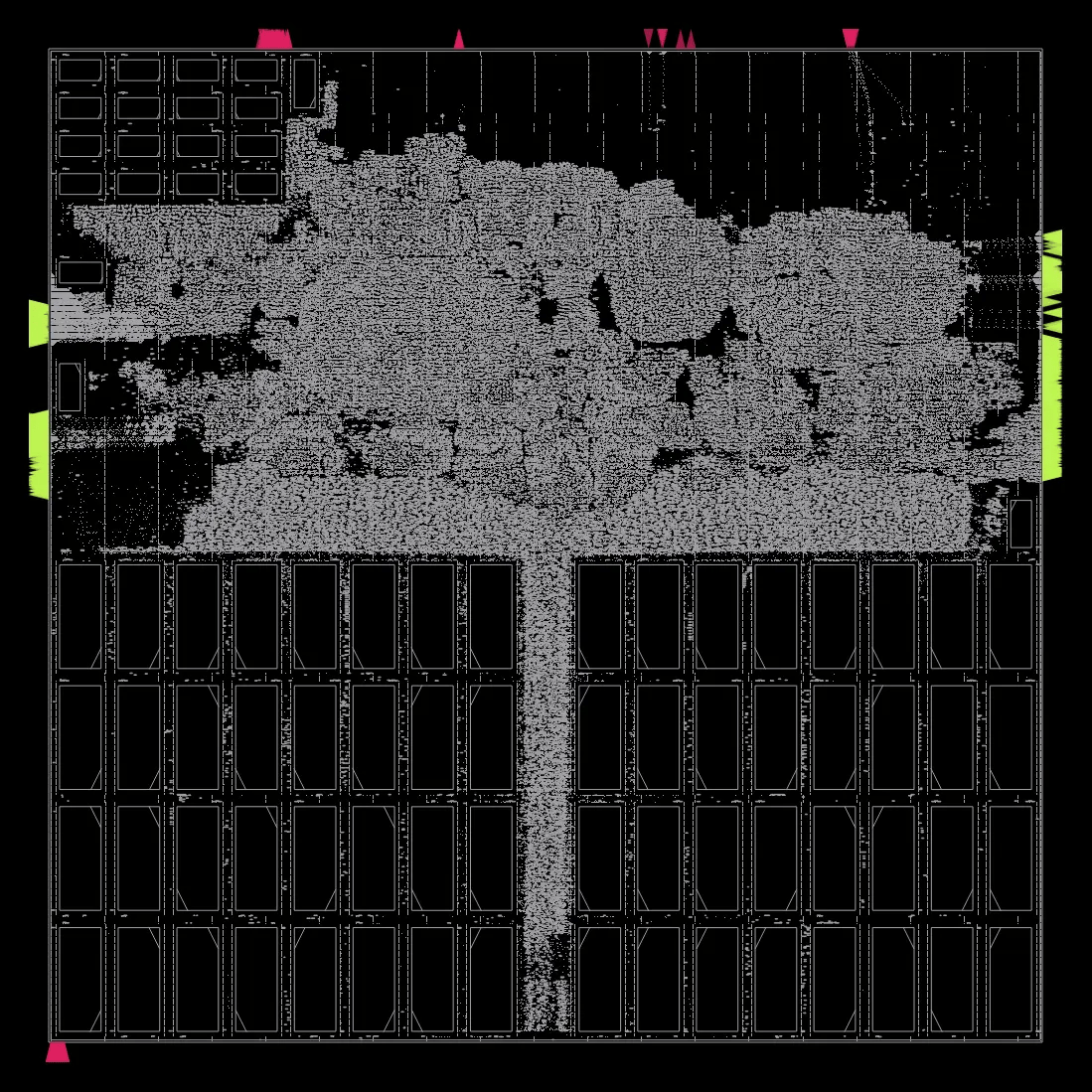

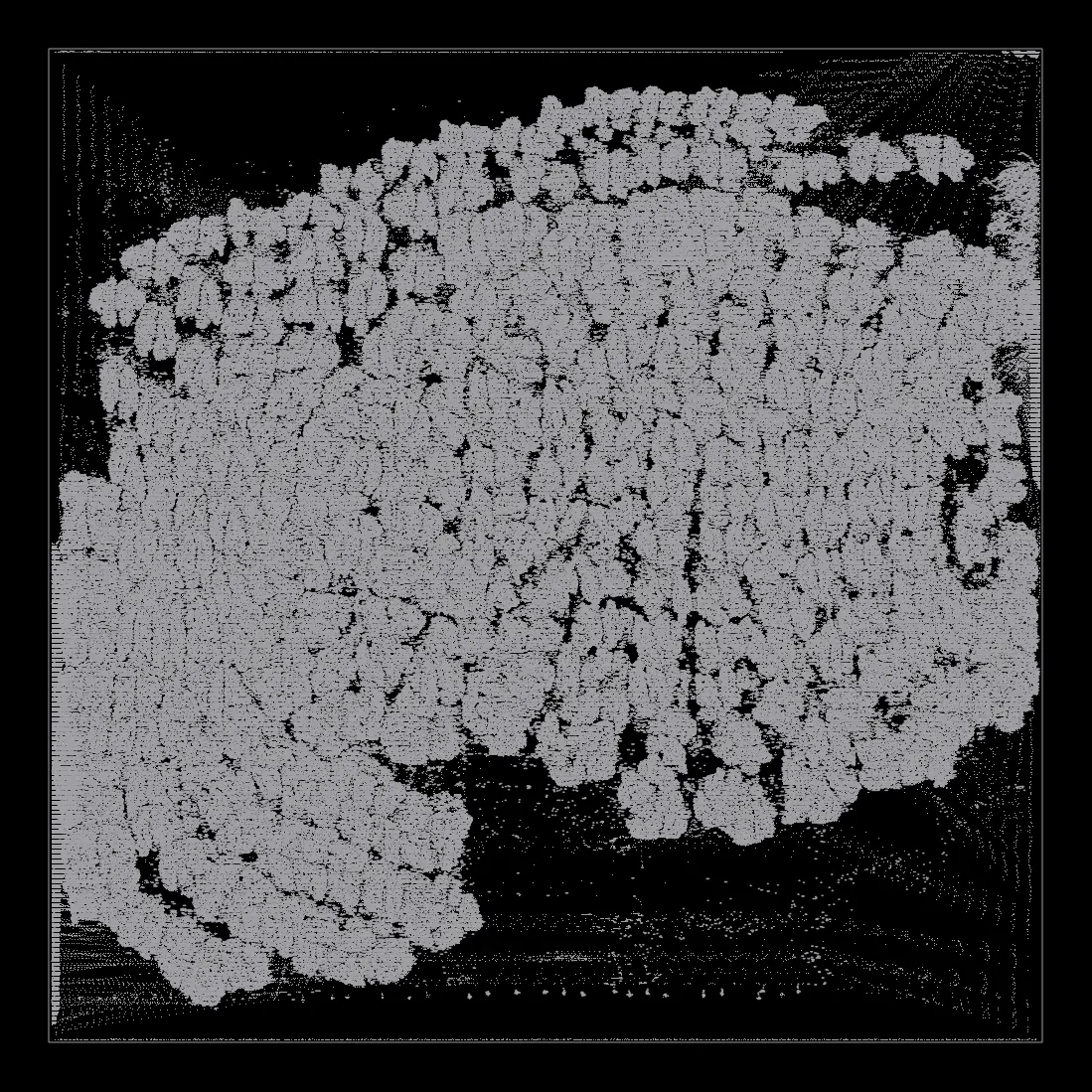

Placement views illustrating the structural diversity across the suite—from small combinational datapaths to large systolic arrays and macro-dense accelerators.

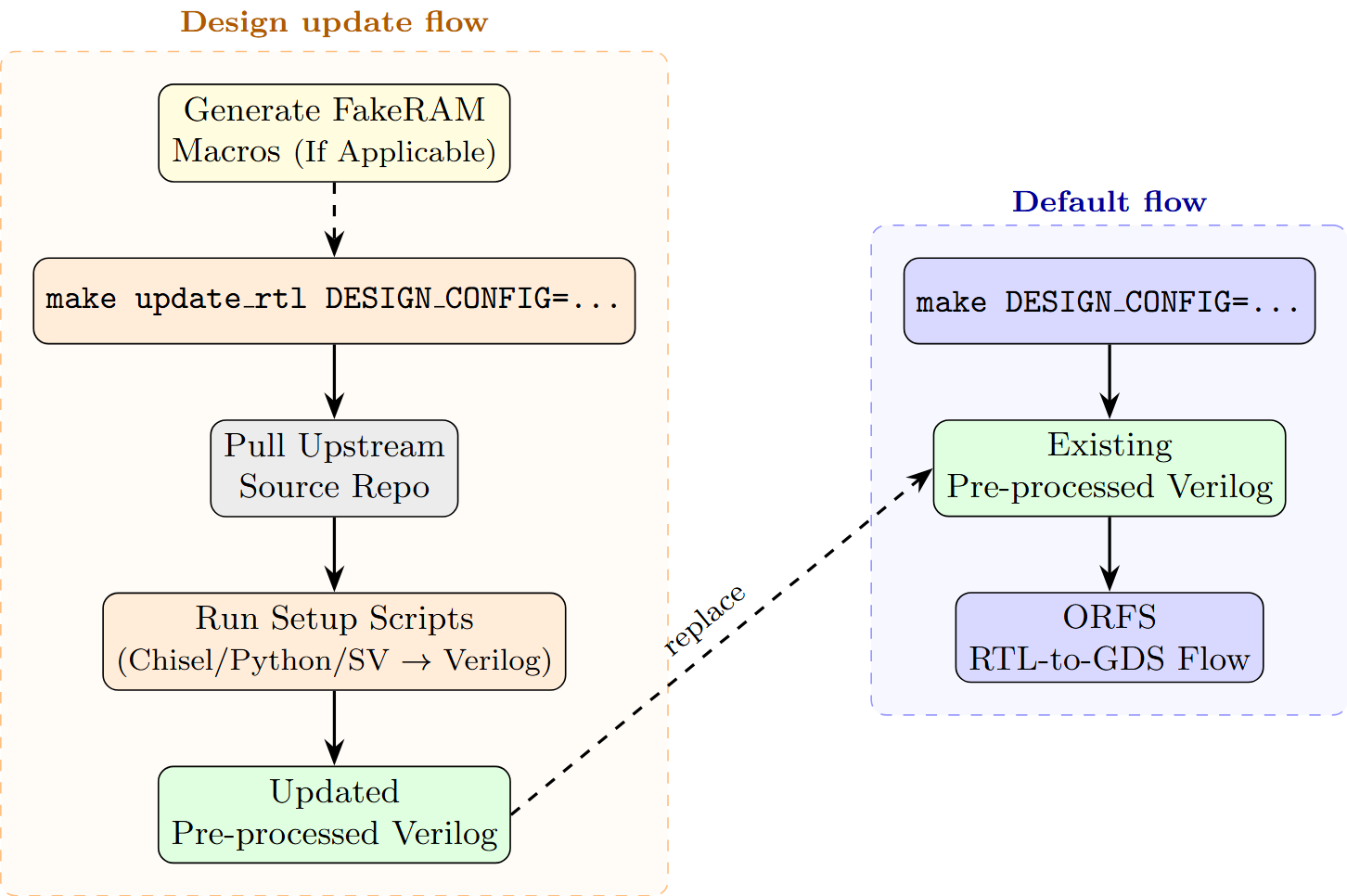

HighTide tracks upstream sources via Git submodules and regenerates Verilog from each design's native language, or uses pre-processed RTL for immediate builds.

Design update path (left) pulls upstream sources and regenerates Verilog from the design's native language. Default path (right) runs pre-existing Verilog through the ORFS RTL-to-GDS flow.

Claude Code skills that automate discovery, integration, and maintenance of benchmark designs.

HighTide includes a set of Claude Code skills—AI-powered slash commands that automate the complex, multi-step processes involved in managing a benchmark suite. These skills handle everything from searching the open-source hardware ecosystem for new candidates to performing full RTL-to-GDSII integration of new designs, reducing what would take hours of manual work to a single command.

Searches the open-source hardware ecosystem for designs that would strengthen the benchmark suite, evaluates them against HighTide's selection criteria, and opens GitHub issues to propose additions.

/find-designs accelerators)Performs the full end-to-end process of adding a new open-source hardware design to the suite, from submodule setup through RTL generation to flow configuration and testing.

Audits all designs and tool dependencies for upstream updates, summarizes what changed, and applies updates while maintaining flow compatibility.

Get up and running in minutes with the Bazel flow.

You need Bazelisk and Docker on an Ubuntu machine.

# Install Bazelisk

sudo apt install perl

sudo wget -O /usr/local/bin/bazel \

https://github.com/bazelbuild/bazelisk/releases/latest/download/bazelisk-linux-amd64

sudo chmod +x /usr/local/bin/bazelgit clone https://github.com/VLSIDA/HighTide.git

cd HighTideRun the full RTL-to-GDSII flow for any design.

# Build a single design

bazel build //designs/asap7/lfsr:lfsr_final

# Build all designs for a platform

bazel build //designs/asap7/...

# Build everything

bazel build //designs/...Check build summaries and QoR reports.

./tools/summary.shSee the latest build results for detailed QoR metrics across all designs and platforms.