# Lecture 10: Gate Delay and Power

Matthew Guthaus Professor UCSC, Computer Science & Engineering <u>http://vlsida.soe.ucsc.edu</u> mrg@ucsc.edu

## **Today's Topics**

- Switched transistor networks

- First-order gate delay model

- Elmore Delay

- Power consumption

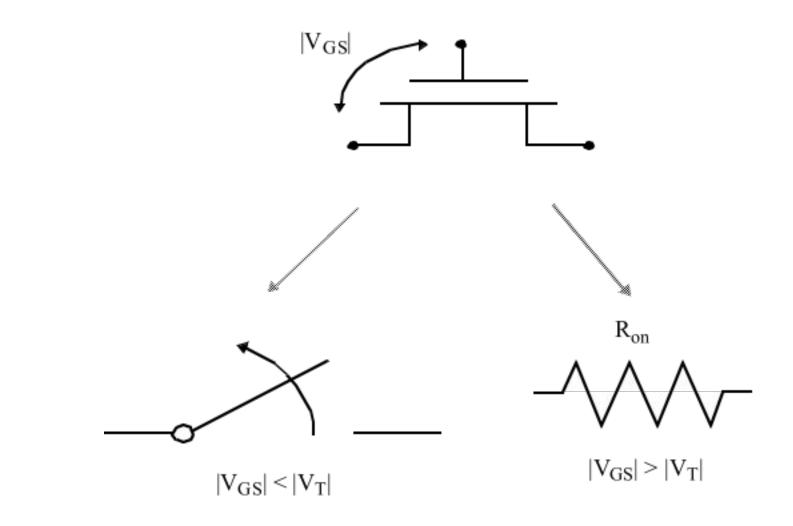

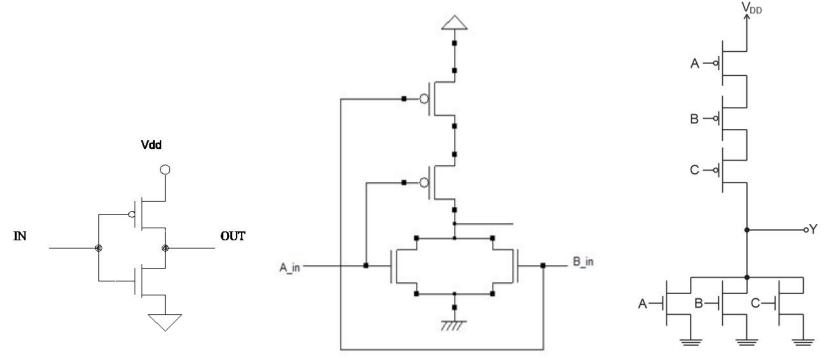

## Switch Model... Again

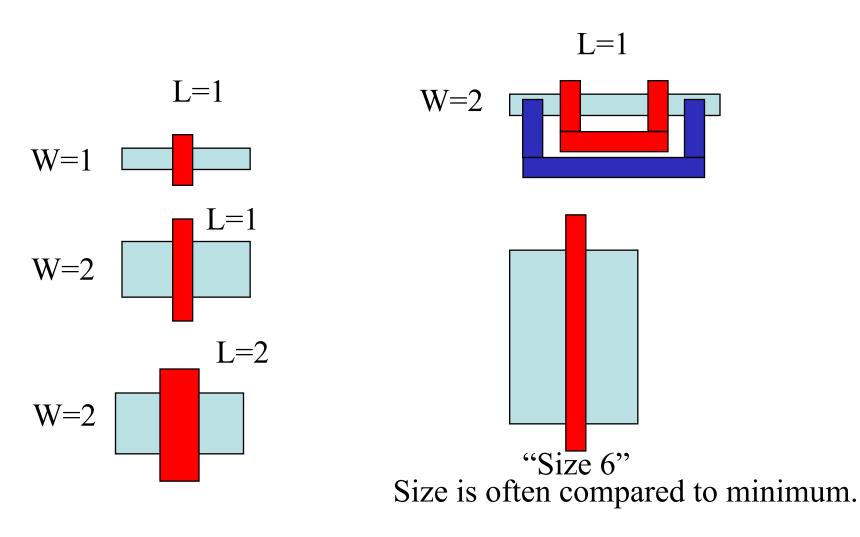

### Transistor W and L

## Transistor as a Switch... Again

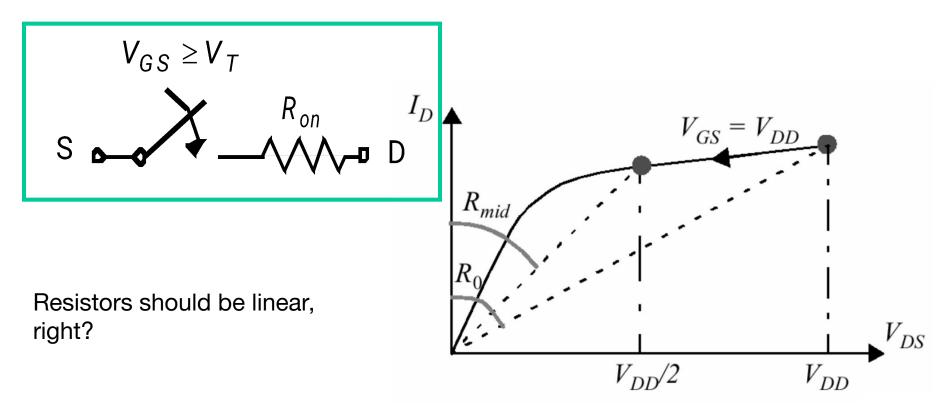

R = Vds / Id Ron ≅ average(R0, Rmid)

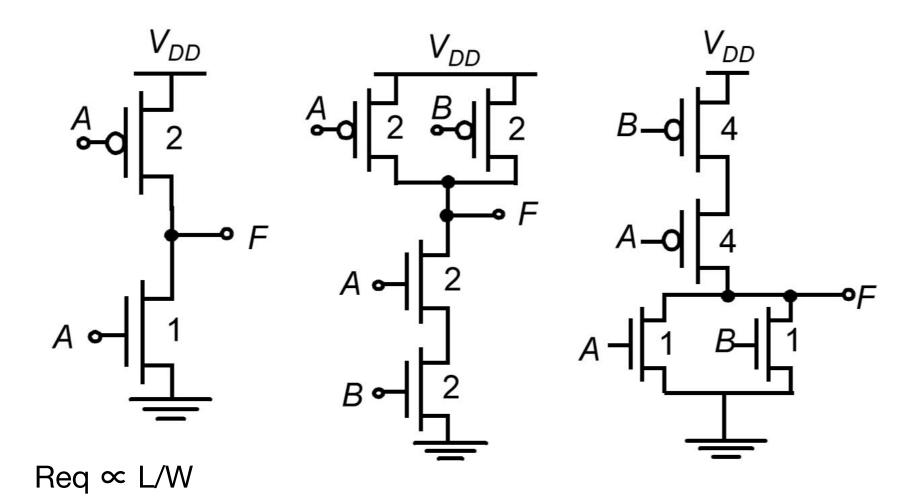

Req ∝ L/W

## Req, W, and L

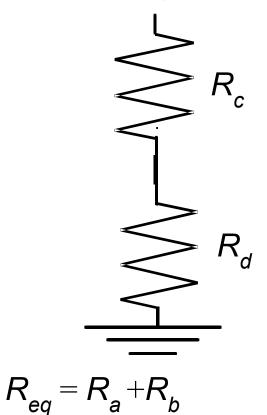

Resistance goes up as L goes up "Resistance in series"

Resistance goes down as W goes up

- "Resistance in parallel"

- Req is proportional to L/W

- Each transistor will have a W and L, if L is not given, it is minimum.

Req ∝ L/W

### **PMOS vs NMOS Resistance**

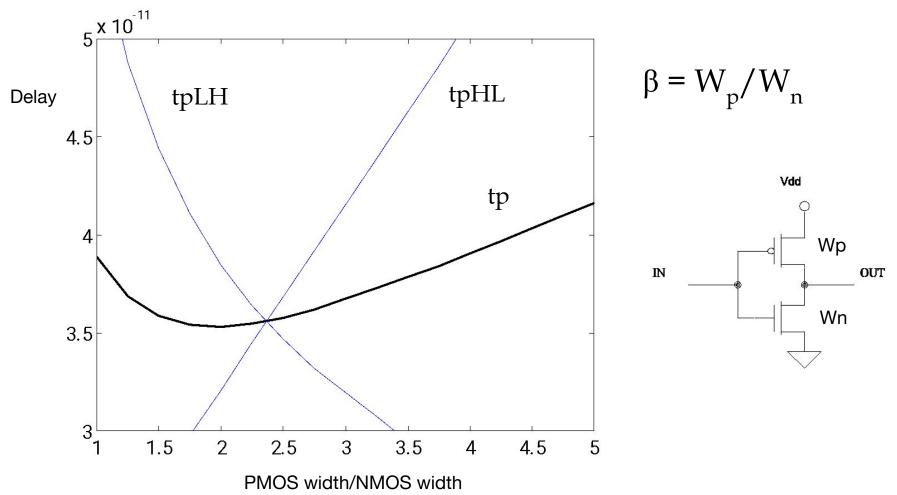

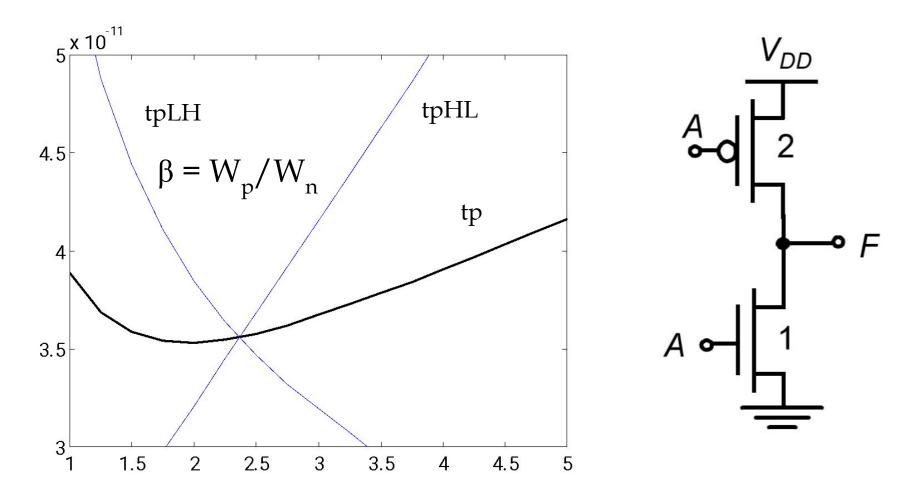

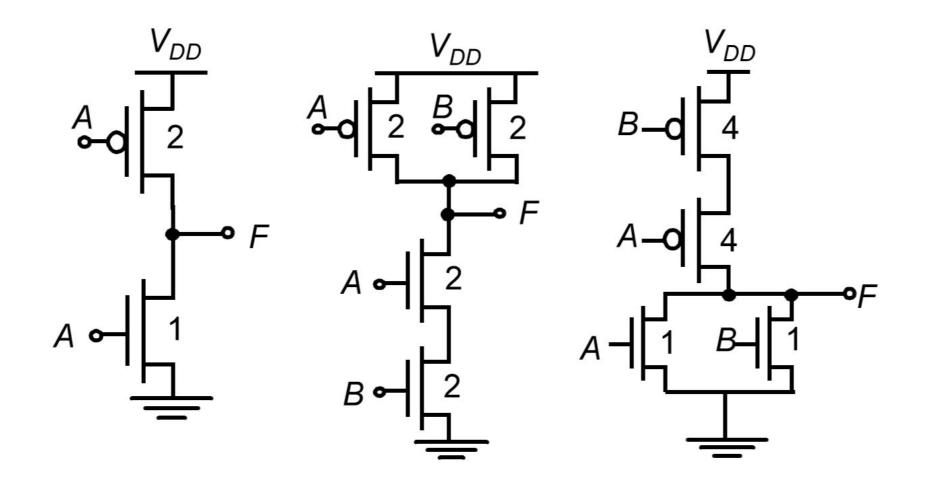

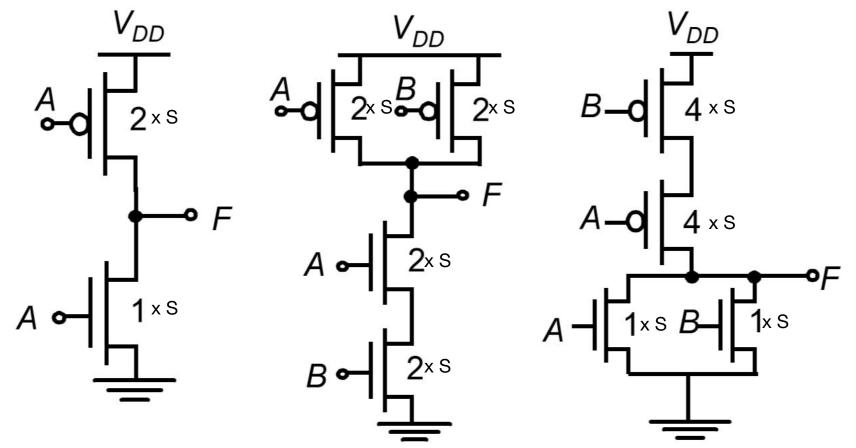

### Vary "ratio" of PMOS to NMOS width

### **Relative resistances**

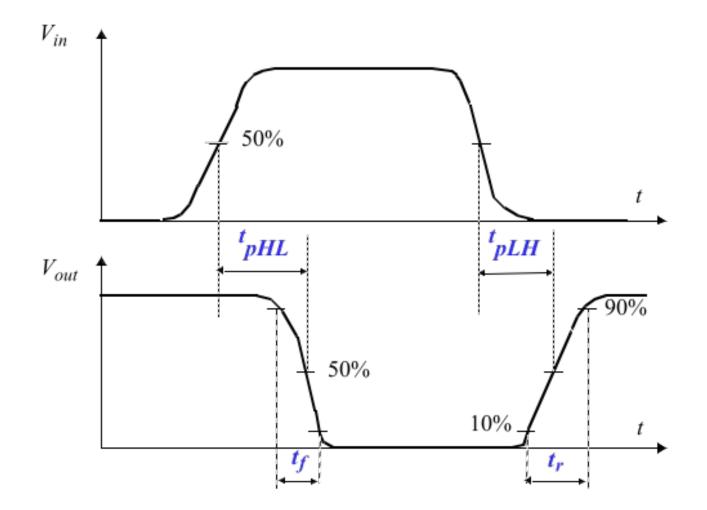

- We often don't need R explicitly, but instead know that:

- 2W has half the R of W

- 4W has 1/4 the R of W

- etc.

- Device types

- PMOS is twice the R of same size NMOS

- PMOS of size 2W is same R as NMOS of size W

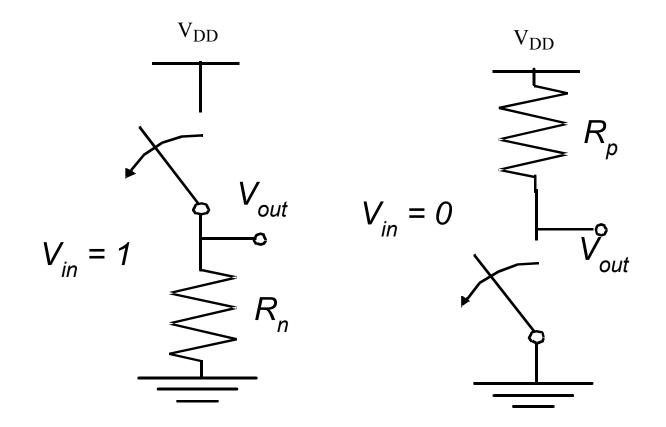

## First Order (Static) Analysis

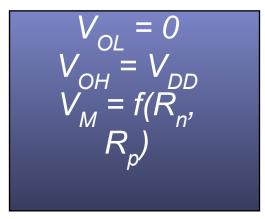

## Delay vs Rise/Fall Definitions

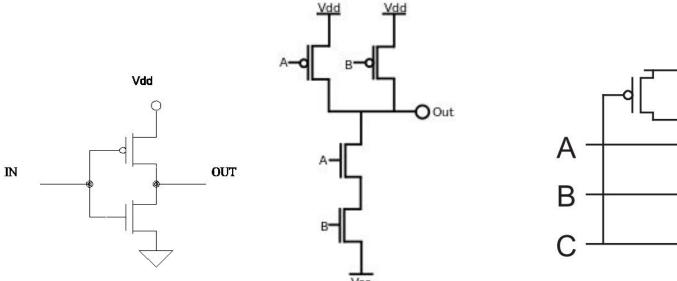

### Switch Model

Which is faster? (Assume same size transistors)

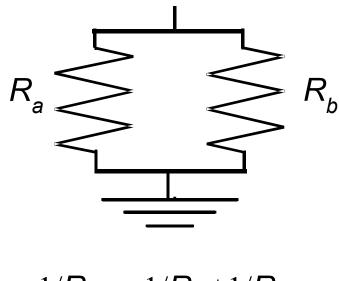

$$1/R_{eq} = 1/R_{a} + 1/R_{b}$$

Sometimes double current

Half the current

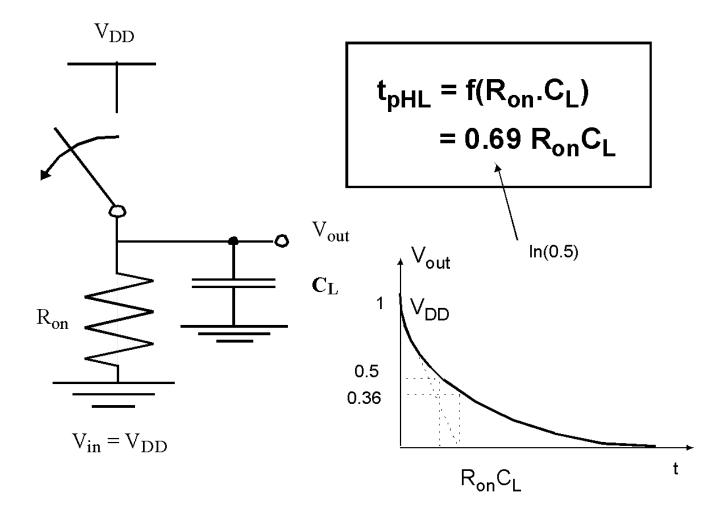

## Transient (Elmore) Delay

### **Intuition Check**

Delay = 0.69RC

What happens if you drive twice the fanout?

What happens if you use a "2x" gate instead of a "1x" (this is drive strength)?

## Pros/Cons of Elmore Delay

- · Cons

- Input is an ideal step

- Assumes resistor model

- Ignores short-circuit current

- Output capacitance computation

- Summing all the fanout and wires is pessimistic

- Most tools use "effective capacitance"

- · Pros

- Simple and intuitive

- Fast

- Good fidelity, but not accuracy

### **PMOS vs NMOS Resistance**

### Vary "ratio" of PMOS to NMOS width

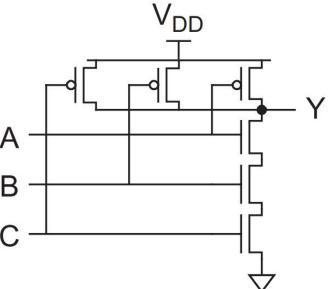

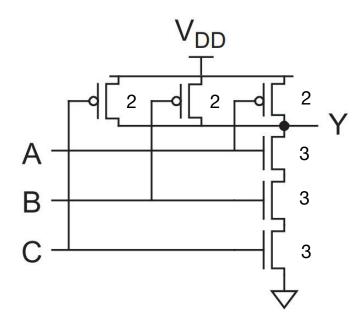

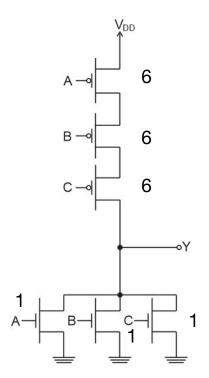

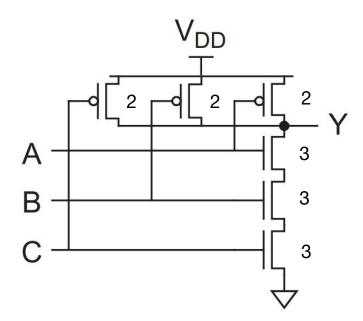

## Scaling of NAND Delay

Series transistors in pull down add up resistance.

More series resistance means more delay.

## Scaling of NOR Delay

Similar to NAND, but pull up delay increases.

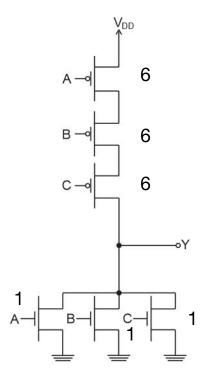

### **Equivalent Width Gates**

### NAND3 and NAND4

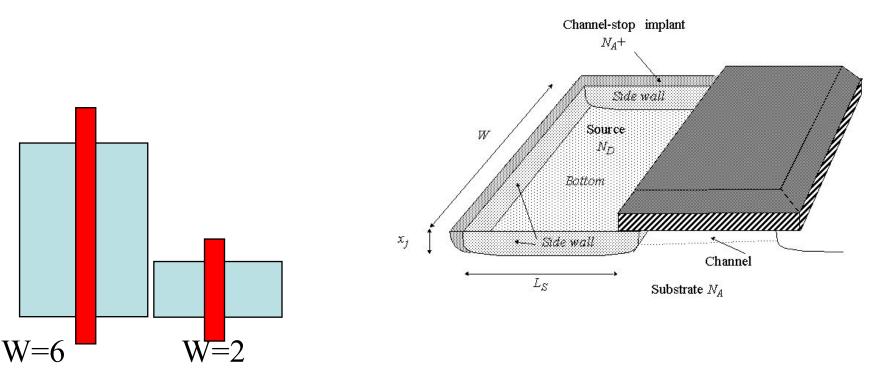

### **Diffusion Capacitance**

## Diffusion capacitance proportional to transistor width

### Capacitance related to perimeter and area

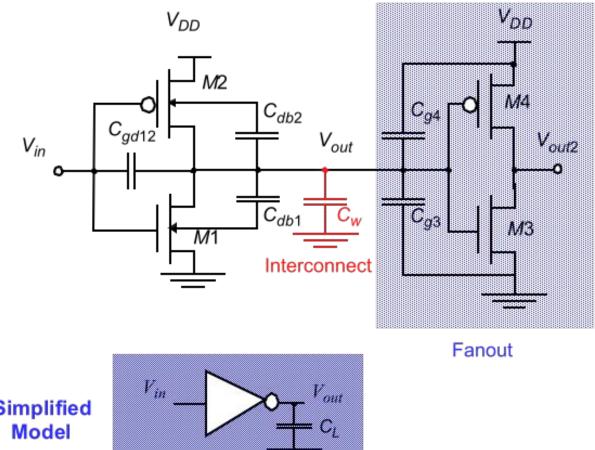

## Visualizing the Capacitances

Simplified

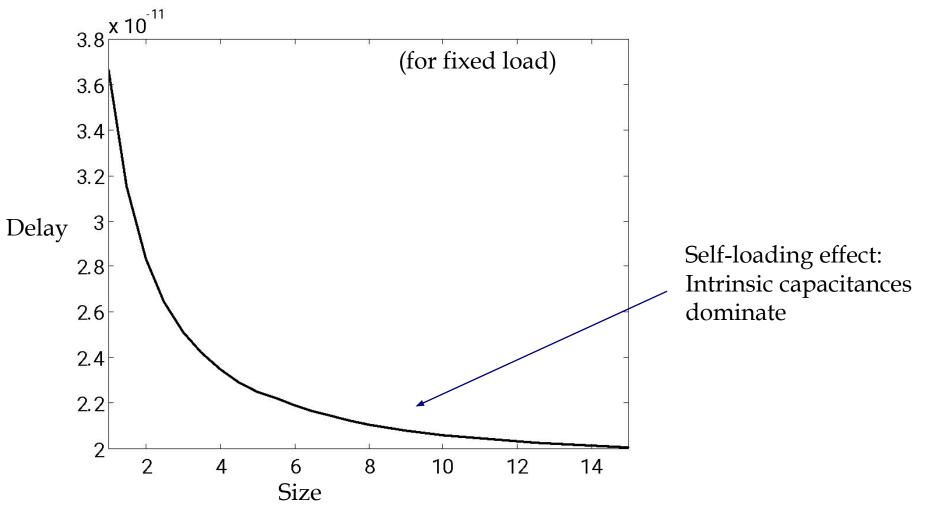

### How much self-loading capacitance?

### How much self-loading capacitance?

### Sizing of Gates

- Relative sizes are preserved

- inv\_1, inv\_2, inv\_4 means S=1, S=2, S=4

## Self Loading

### Consider a gate driving a fixed output cap.

### Where does power go in CMOS?

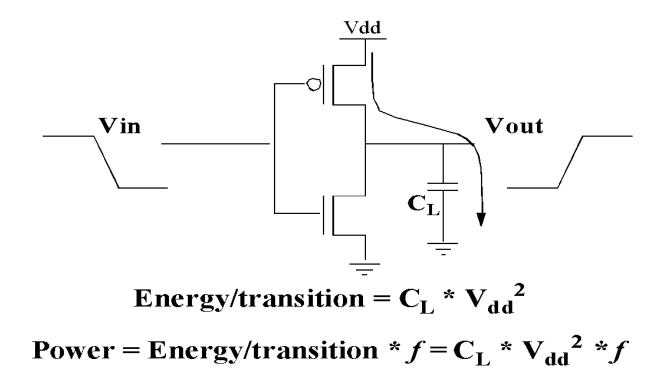

Dynamic Power Consumption

**Charging and Discharging Capacitors**

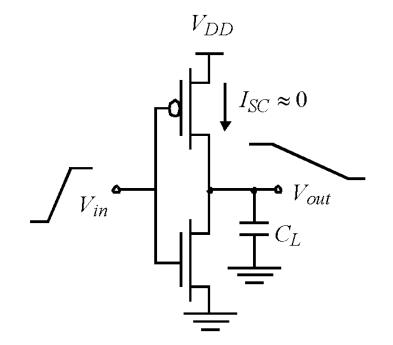

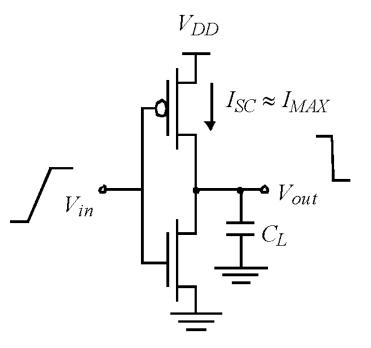

#### Short Circuit Currents

Short Circuit Path between Supply Rails during Switching

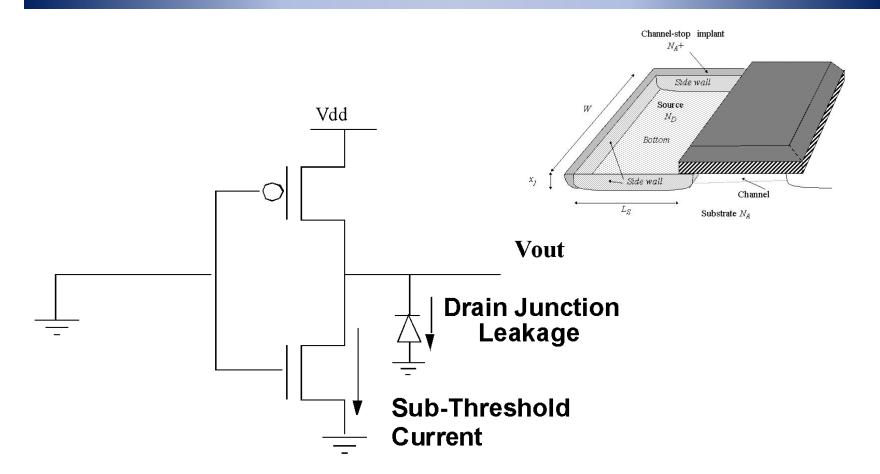

#### • Leakage

Leaking diodes and transistors

### Power: Dynamic

- Not a function of transistor sizes!

- Need to reduce  $C_L$ ,  $V_{dd}$ , and f to reduce power.

### **Power: Leakage**

**Sub-Threshold Current Dominant Factor**

### **Power: Short Circuit**

## Both PMOS and NMOS are "on" while a signal is transitioning

Large capacitive load

Small capacitive load

## (Some) Low Power Techniques

- Reduce capacitance

- Use smaller size gates

- Shorten wires

- Reduce switching

- Lower frequency

- Logic gating

- Lower vdd

- Increase Vth (lowers leakage)

### **Power Reports**

### OpenLane/designs/picorv32a/runs/CLASS/r eports/signoff/31-rcx\_sta.power.rpt

|              | ===== Typical     | Corner =====      |                  |          |         |

|--------------|-------------------|-------------------|------------------|----------|---------|

| Group        | Internal          | Switching         | Leakage          | Total    |         |

|              | Power             | Power             | Power            | Power    | (Watts) |

| sequential   | 3.96e-03          | 1.51e-03          | 1.35e-08         | 5.48e-03 | 25.5%   |

| ombinational | 6.79e-03          | 9.23e-03          | 5.99e-08         | 1.60e-02 | 74.5%   |

| lacro        | 0.00e+00          | 0.00e+00          | 0.00e+00         | 0.00e+00 | 0.0%    |

| 'ad          | 0.00e+00          | 0.00e+00          | 0.00e+00         | 0.00e+00 | 0.0%    |

|              |                   |                   |                  |          |         |

| Total        | 1.08e-02<br>50.0% | 1.07e-02<br>50.0% | 7.33e-08<br>0.0% | 2.15e-02 | 100.0%  |

### Next Lecture

Interconnect