# Lecture 09: Static Timing Analysis

Matthew Guthaus Professor UCSC, Computer Science and Engineering <u>http://vlsida.soe.ucsc.edu</u> mrg@ucsc.edu

## Today's Topics

- Timing Constraints

- Long paths

- Short paths

- Static Timing

- Timing Corners

# Why Clocks?

- Clocks provide the means to synchronize

- By allowing events to happen at known timing boundaries, we can sequence these events

- Greatly simplifies building of state machines

- No need to worry about variable delay through combinational logic (CL)

- All signals delayed until clock edge (clock imposes the worst case delay)

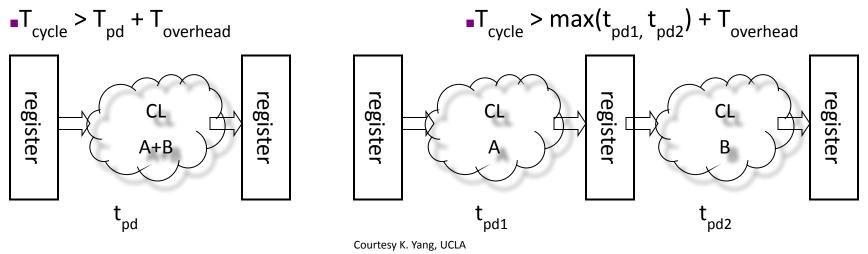

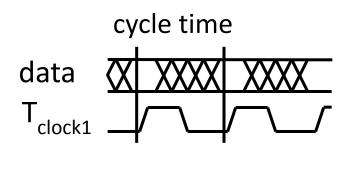

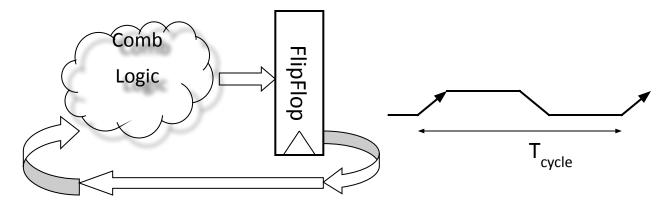

## Clock Cycle Time

- Cycle time is determined by the delay through the CL

- Signal must arrive before the latching edge

- If too late, it waits until the next cycle

- Synchronization and sequential order becomes incorrect

- Constraint: Tcycle > Tprop\_delay\_through\_CL + Toverhead

Example: 3.0 GHz Pentium-4

Tcycle = 333ps

- Can change circuit architecture to obtain smaller Tcycle

# Pipelining

- For dataflow:

- Instead of a long critical path, split the critical path into chunks

- Insert registers to store intermediate results

- This allows 2 waves of data to coexist within the CL

- Can we extend this ad infinitum?

- Overhead eventually limits the pipelining

- E.g., 1.5 to 2 gate delays for latch or FF

- Granularity limits as well

- Minimum time quantum: delay of a gate

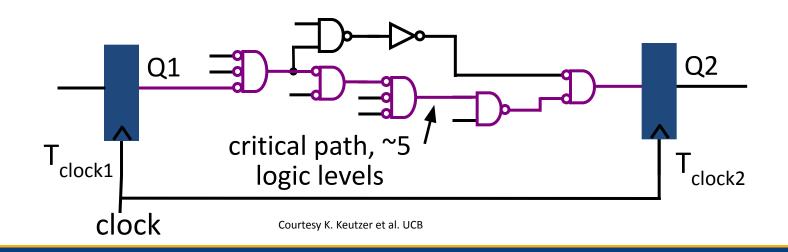

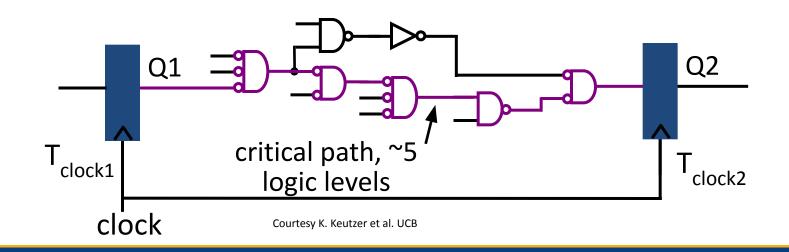

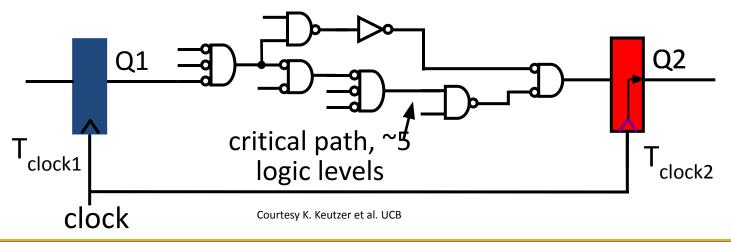

#### Let's Revisit Cycle Time and Path Delay

- Cycle time (T) cannot be smaller than longest path delay (T<sub>max</sub>)

- Longest (critical) path delay is a function of:

- Total gate

- Wire delays

- (Logic levels)

$T_{max} \leq T$

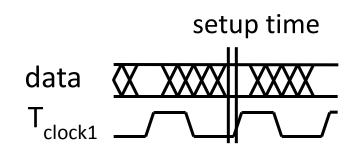

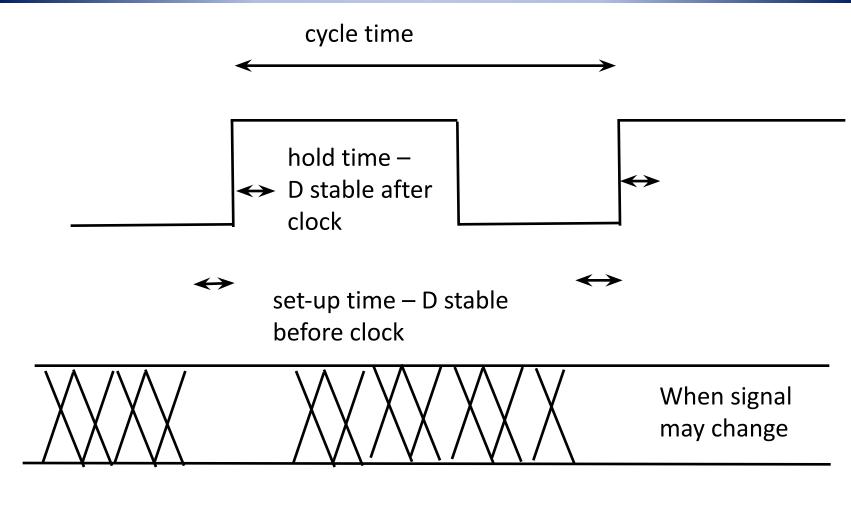

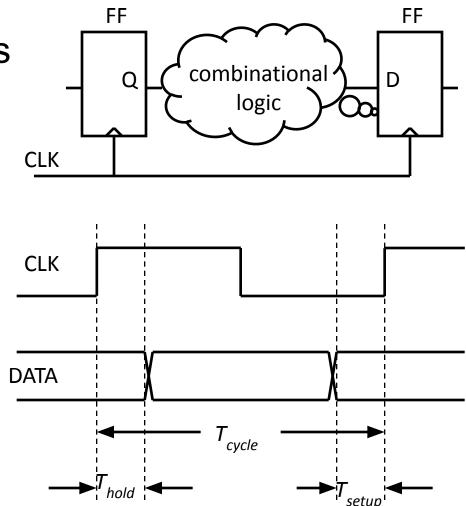

#### Cycle Time - Setup Time

- For FFs to correctly capture data, must be stable for:

- Setup time (T<sub>setup</sub>) before clock arrives

$T_{max} + T_{setup} \leq T$

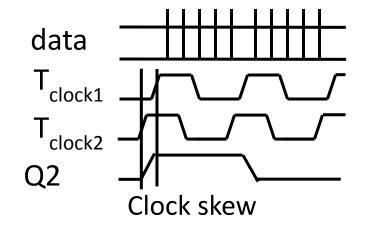

#### Cycle Time – Clock Skew

- If clock network has unbalanced delay – clock skew

- Cycle time is also a function of clock skew (T<sub>skew</sub>)

$$T_{max} + T_{setup} + T_{skew} \le T$$

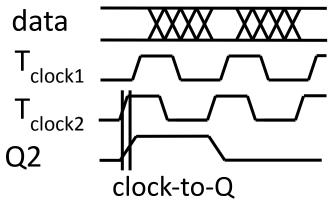

#### Cycle Time – Flip-Flop Delay (Clock to Q)

• Cycle time is also a function of propagation delay of FF ( $T_{clk-to-Q}$  or  $T_{c2q}$ )

•  $T_{c2q}$ : time from arrival of clock signal till change at FF output  $T_{max} + T_{setup} + T_{skew} + T_{clk-to-Q} \le T$

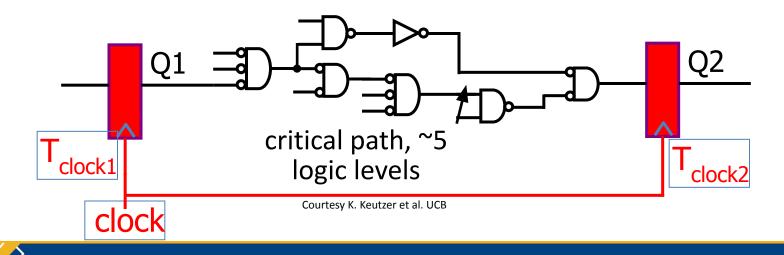

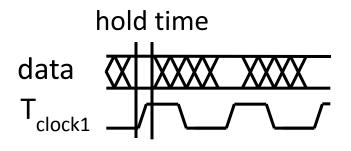

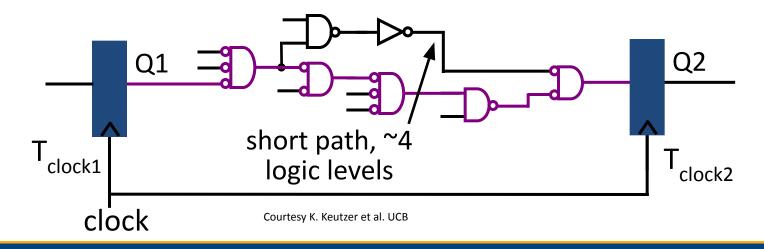

#### Min Path Delay - Hold Time

- For FFs to correctly latch data, data must be stable during:

- Hold time (T<sub>hold</sub>) after clock arrives

- Determined by delay of shortest path in circuit (T<sub>min</sub>) and clock skew (T<sub>skew</sub>)

```

T_{min} \geq T_{hold} + T_{skew}

```

#### Setup, Hold, Cycle Times

Example of a single phase clock

Courtesy K. Keutzer et al. UCB

## Positive or Negative Clock Skew?

- Usually defined by receiving minus launching clock

- However, often a single value or "budget" can be assumed of Tskew

- Used as "worst case" for all pairs of flops

- Especially if pre-CTS (i.e. during synthesis and placement)

- Technically...

- Positive skew helps setup paths

- Negative skew helps hold paths

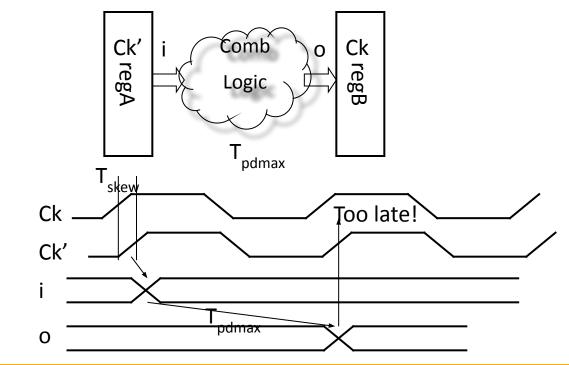

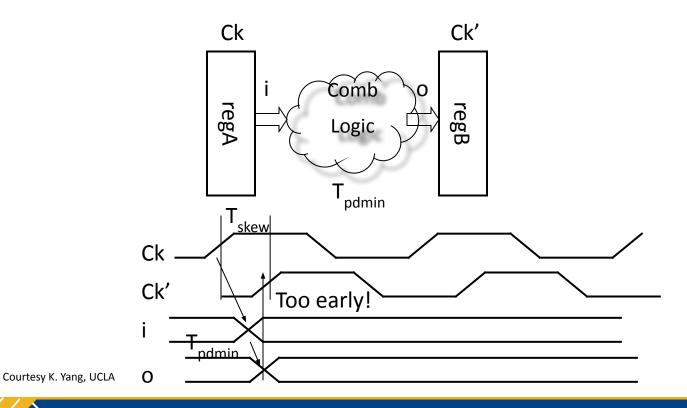

#### Timing Constraints for Edge-Triggered FFs

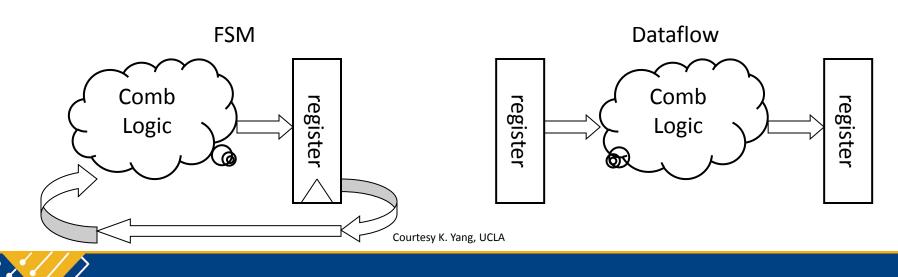

Courtesy K. Yang, UCLA

- $Max(T_{pd}) < T_{cycle} T_{setup} T_{c2q} T_{skew}$ - Delay is too long for data to be captured

- $Min(T_{pd}) > T_{hold} T_{c2q} + T_{skew}$

- Delay is too short and data can race through, skipping a state

### Example of T<sub>pdmax</sub> Violation

- Suppose there is skew between the registers in a dataflow (regA after regB)

- "j" gets its input values from regA at transition in Ck"

- CL output "o" arrives after Ck transition due to skew

- To correct this problem, can *increase* cycle time

Courtesy K. Yang, UCLA

### Example of T<sub>pdmin</sub> Violation: Race Through

- Suppose clock skew causes regA to be clocked before regB

- "i" passes through the CL with little delay (tpdmin)

- "o" arrives before the rising Ck' causes the data to be latched

- Cannot be fixed by changing frequency  $\Box$  have rock instead of chip

#### Summary: Timing Constraints

- Synchronous design

= combinational logic

+ sequential elements

- For each flip-flop:

- $= T_{max} + T_{setup} < T_{cycle} T_{skew}$

- $\blacksquare T_{min} > T_{hold} + T_{skew}$

- T<sub>max</sub>: longest data propagation path delay

- T<sub>min</sub>: shortest data propagation path delay

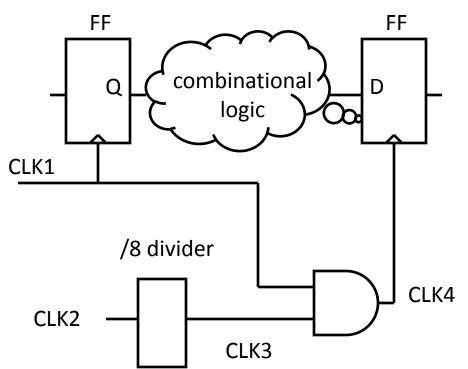

# **Clock Identification**

- Partition the design

- Clock network

- Clock definition

- Derived clock

- Clock groups

- Clock delay (skew) calculation

- Timing constraints exist between clocks with a common divisor frequency

- Data paths with timing constraints

### **STA Overview**

- Questions it can answer

- Can my circuit run at X Ghz?

- What is the worst path of my circuit?

- Do I have any hold violations?

- Static vs Dynamic Timing

- For n inputs and m FF bits, there are 2<sup>(m+n)-1</sup> possible patterns.

- This cannot be exhaustively tested!

- Incremental timing for optimization

- If I have a timing problem, how do I fix it?

- Corner analysis for temperature, process, etc.

- Will my circuit work under all conditions?

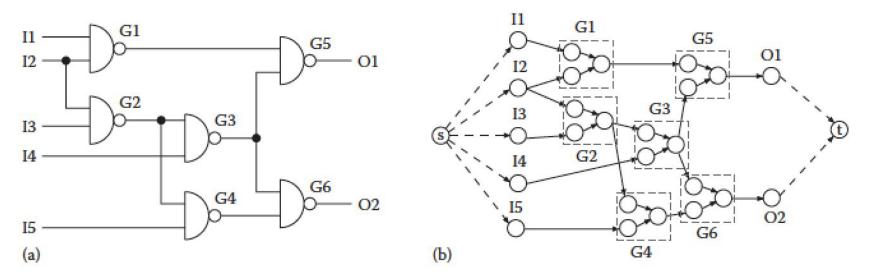

### **Circuit Representation**

- Directed Acyclic Graph (DAG)

- Circuit is broken at sequential elements (e.g. FFs)

- s can be circuit input or FF output (input delay)

- t can be circuit output or FF input (setup time)

- Edges are gate or wire delays

- Nodes are pins on gates or inputs/outputs

### Gate Delay Models

- Discussed in Cell Library lecture

- Use as inputs:

- output load

- input signal slew (transition time)

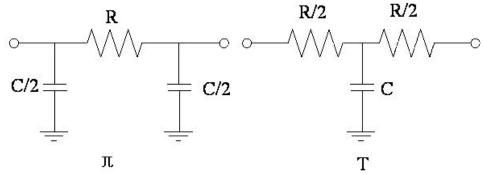

#### Capacitance

- Lumped capacitance

- Self loading capacitance

- Fanout gate pin capacitances

- Fanout wire substrate/coupling capacitances

- More on crosstalk later

- Effective capacitance

- Not all capacitance is seen at the output due to "resistive shielding"

- Usually a Pi (or T) model

## Wire Delay Models

- Wire delay from driver pin to each fanout gate pin

- More in Interconnect lecture...

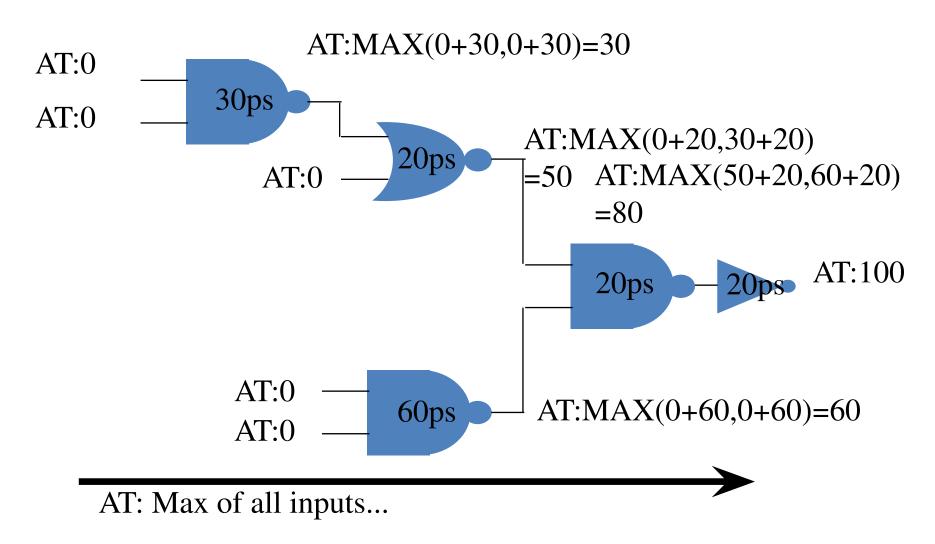

## **Block Based Timing Analysis**

- Ignores function of gates

- Propagates the worst cumulative delay from inputs to outputs

- Based on 1966 project management technique: Program Evaluation and Review Technique (PERT)

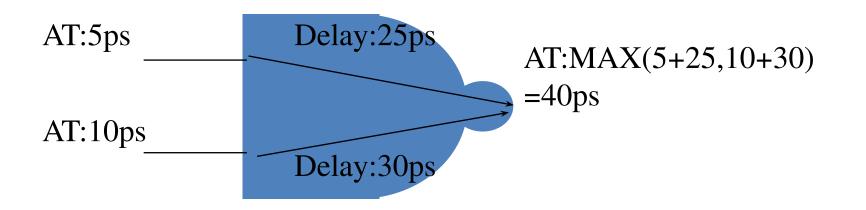

### **Arrival Time**

- Typically compute for (Rise,Fall) x (Early,Late)

- Also propagate slew (delay needs the slew)

# Assume all inputs come from a DFF set\_driving\_cell -lib\_cell \$DFF\_CELL [all\_inputs] set\_input\_delay \$DFF\_CKQ -clock \$CLK [remove\_from\_collection [all\_inputs] [list \$CLK \$RST]]

### **Arrival Time**

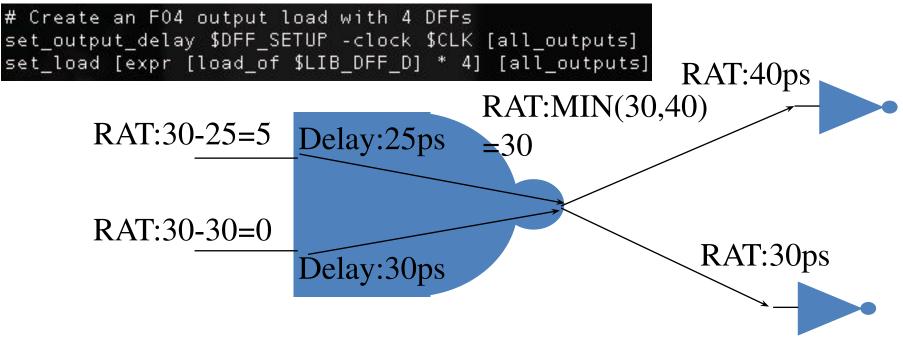

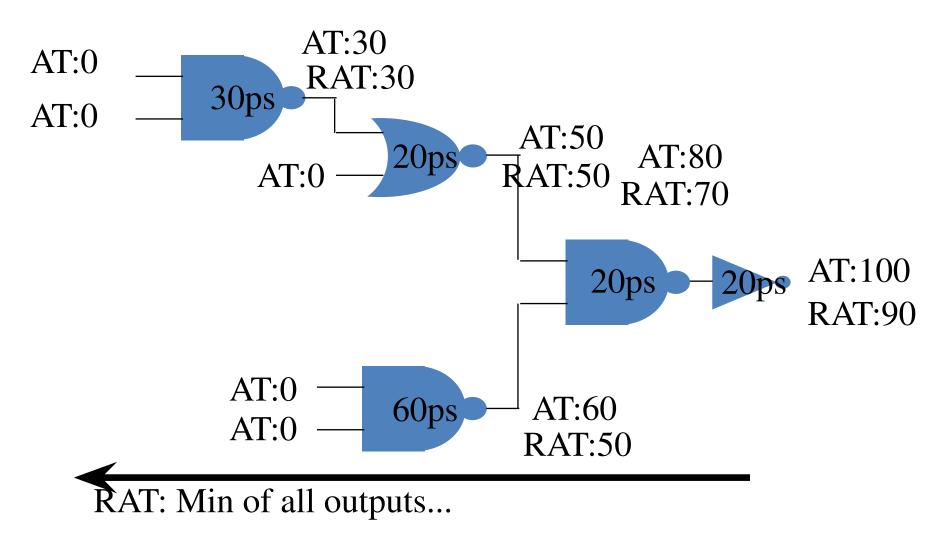

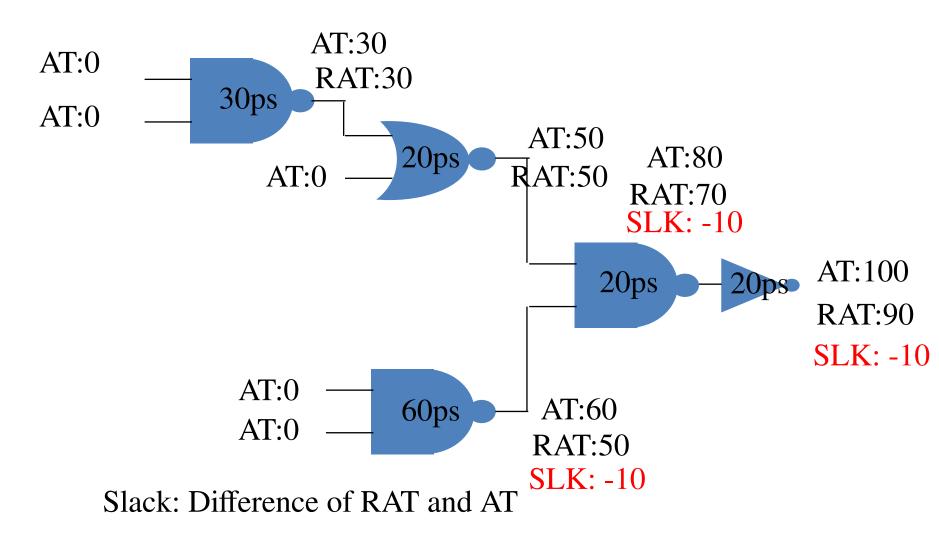

## **Required Arrival Time**

- Time signal is needed at a point to get to output by constrained time

- Late checks set RAT to clock period at outputs/FFs

- Early checks set RAT to hold time at output/FFs

- Typically compute for (Rise,Fall) x (Early,Late)

#### **Required Arrival Time**

#### Slack: RAT-AT

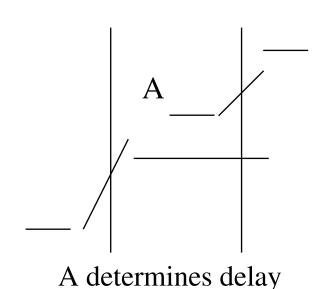

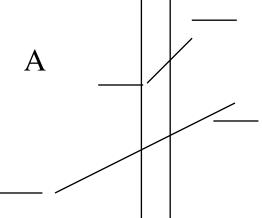

## Transition Time/Slew Propagation

- The above talked about wire and gate delays, but we also must propagate slew to every wire.

- What slew do we propagate?

- Biggest slew of all inputs? Could be conservative if it is too early.

- Latest arriving signal? This may not determine the worst delay.

- Selectable in STA:

- set timing\_slew\_propagation\_mode worst\_value

## Slew Challenge Example

- Remember: Delay is 50%-50%, Slew is 10%-90%

- Signal A may have a bigger delay, but B has such a bad slew that it determines the output delay

B determines delay despite arriving earlier than A

### **Other Delay Assumptions**

- Single input switching assumption

- Could turn on multiple paths in CMOS network which result in ramp with two different slopes

- Switching a second input could add internal gate capacitance to output

- Slew is a single ramp

- If second path in network turns on...

- Inductance can have non-monotonic behavior

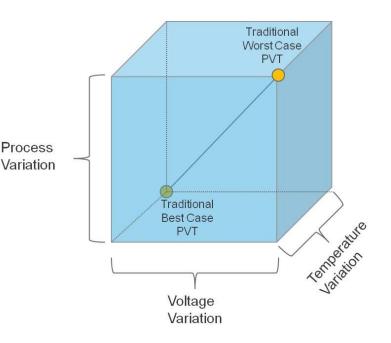

## **Timing Corners**

- The previous gate and wire delays can also have different "corners"

- Temperature

- Process (PMOS/NMOS variation)

- Supply Voltage

- Worst case corners

- Early will want to use the fastest process, highest supply, lowest temperature

- Late will want to use the slowest process, lowest supply, highest temp

- Worst case corners are becoming too pessimistic!

### Demo in OpenRoad/OpenLane

Text STA reports Hold Setup Corners GUI browser