# Lecture 07: OpenLane

Matthew Guthaus Professor UCSC, Computer Science & Engineering <u>http://vlsida.soe.ucsc.edu</u> mrg@ucsc.edu

### Quiz 1

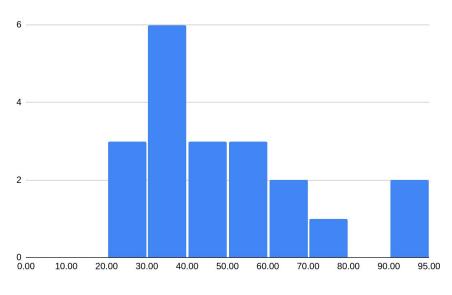

CSE 122 47% average

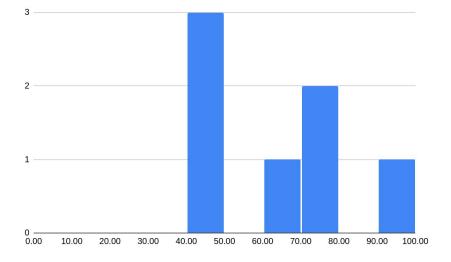

CSE 222A 64% average

## Partial Credit Quiz 1

Resubmit PDF as quiz1.pdf to git repo. Will provide blank quiz as well in Slack.

Up to 20% partial credit.

#### **Due this Friday 5pm**

## HW1 Part 2b Resubmit

#### We didn't have all the DRC checks enabled! In demo klayout/drc/sky130.lydrc change FEOL from false to true.

# enable / disable rule groups

FEOL = false # front-end-of-line checks

BEOL = true # back-end-of-line checks

OFFGRID = true # manufacturing grid/angle checks

# This was why drc4.gds also had an LVS issue. One error wasn't flagged.

**Resubmit the GDS by Sunday 4/30 5pm.** No penalty. No need to describe additional errors in part 2a.

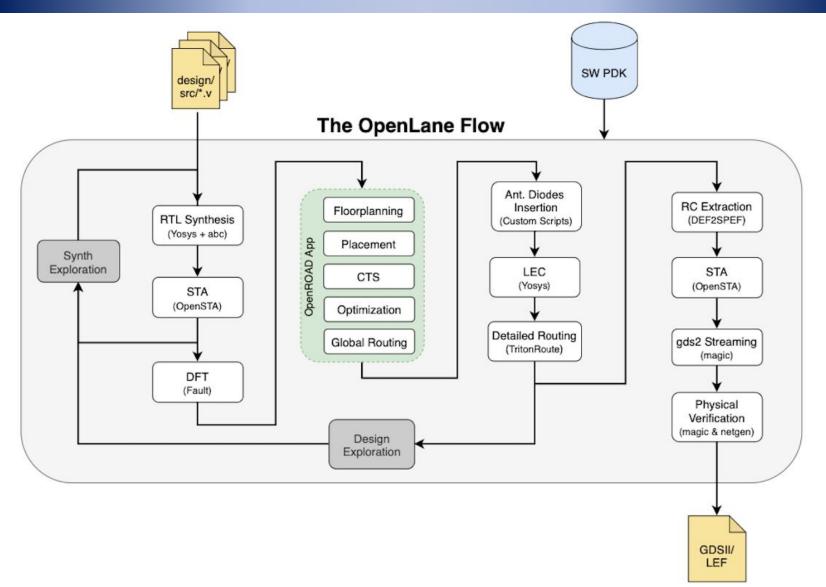

# Today's Lecture

- TCL

- Flow Steps and Control

- Design Directory Structure

- · OpenRoad GUI

- Project Configuration

- Design Space Exploration

https://openlane.readthedocs.io/

# Tool Command Language (TCL)

- https://www.tcl.tk/man/tcl8.5/tutorial/tcltutorial.html

- Scripting (interpreted) language

- Loops, variables, etc.

- Regular expressions

- Tool commands are added

- Links to C, C++, etc. code

- Used by almost every commercial EDA tool!

- OpenLane/scripts/tcl\_commands

- OpenLane interface sets up a lot of "defaults" in the technology

- Examples: init\_floorplan, place\_io, run\_sta, etc.

- OpenLane/scripts/openroad

- OpenRoad provides commands for different tools

- clock\_tree\_synthesis, detailed\_placement

# Flow Steps

## **Flow Control**

#### flow.tcl

|            | set steps [dict create \                                           |  |  |  |  |  |

|------------|--------------------------------------------------------------------|--|--|--|--|--|

|            | "synthesis" "run_synthesis" \                                      |  |  |  |  |  |

| Arguments: | "floorplan" "run_floorplan" \                                      |  |  |  |  |  |

| -design    | "placement" "run_placement_step" \                                 |  |  |  |  |  |

| -uesign    | "cts" "run_cts_step" \                                             |  |  |  |  |  |

| -from      | "routing" "run_routing_step" \                                     |  |  |  |  |  |

| -to        | "parasitics_sta" "run_parasitics_sta_step" \                       |  |  |  |  |  |

| -10        | "eco" "run_eco_step" \                                             |  |  |  |  |  |

| -tag       | "diode_insertion" "run_diode_insertion_2_5_step" \                 |  |  |  |  |  |

| -tag       | "irdrop" "run_irdrop_report_step" \                                |  |  |  |  |  |

| -overwrite | "gds_magic" "run_magic_step" \                                     |  |  |  |  |  |

|            | "gds_klayout" "run_klayout_step" \                                 |  |  |  |  |  |

|            | "lvs" "run_lvs_step \$LVS_ENABLED " \                              |  |  |  |  |  |

|            | "drc" "run_drc_step \$DRC_ENABLED " \                              |  |  |  |  |  |

|            | "antenna_check" "run_antenna_check_step \$ANTENNACHECK_ENABLED " \ |  |  |  |  |  |

|            | "cvc_rv" "run_erc_step"                                            |  |  |  |  |  |

|            |                                                                    |  |  |  |  |  |

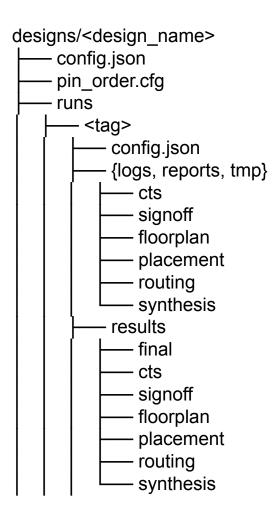

## **Design Directory Structure**

- Each design has a config.tcl (older) or config.json (preferred)

- Optional pin placement file

- Optional SDC (Synopsys Design Constraints) file

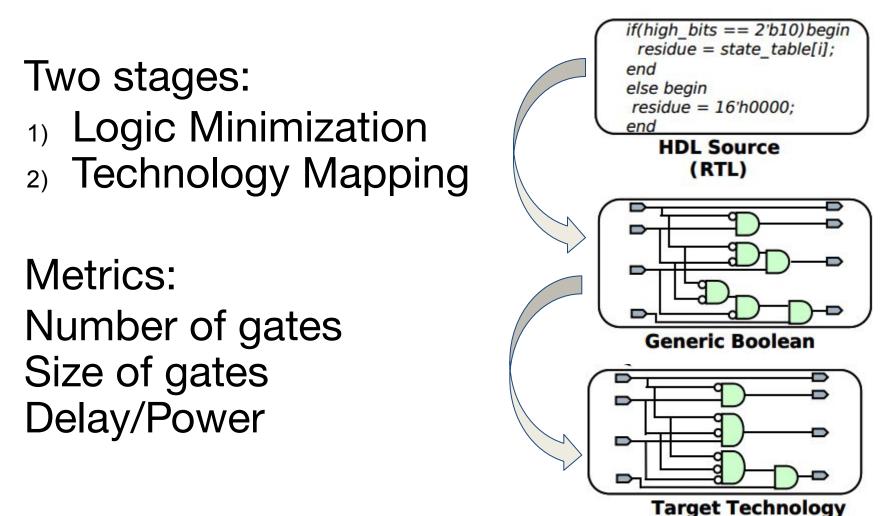

## Synthesis

Goal: Map Verilog to gate-level netlist

## **Standard Cell Libraries**

#### Fixed height cells Different logic functions (nand, mux, aoi221) Sequential cells (flip-flops and latches)

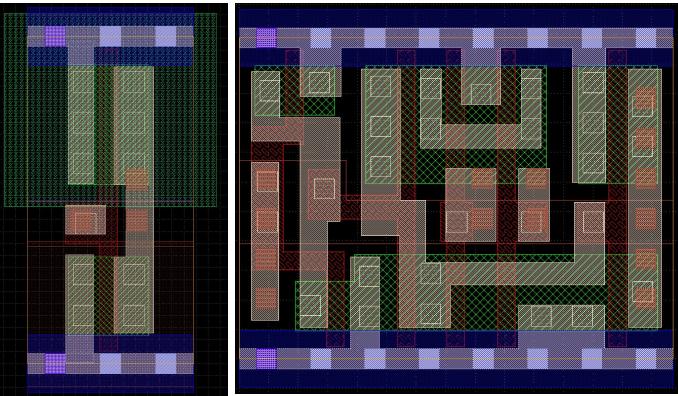

# Floorplan

Goal: Create the high-level chip/block plan

#### Stages:

- 1) Determine chip/block area

- 2) IO placement

- 3) Block placement

- 4) Define standard cell rows

- 5) Power planning

Metrics: Area Area utilization

### Placement

#### Goal: Determine locations of all logic gates

#### Stages:

- 1) Global Placement

- 2) Detailed Placement

Metrics: Minimize wire length Minimize congestion Minimize timing

|   | * * * * * * * * * * * * * | , , , , , , , , , , , | * * * * * * * * * | ¥ ¥ ¥ ¥ |

|---|---------------------------|-----------------------|-------------------|---------|

|   | - <b> </b>                |                       | wi (重要) Wi        |         |

| ł |                           |                       |                   |         |

|   |                           |                       |                   |         |

| • |                           |                       |                   |         |

|   |                           |                       |                   |         |

|   |                           |                       |                   |         |

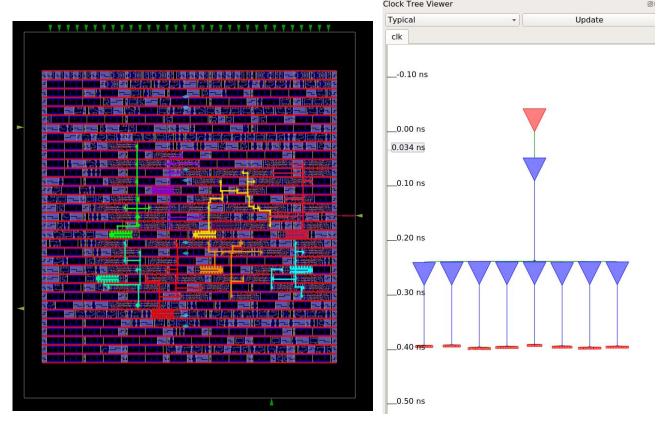

#### CTS

# Goal: Determine clock buffer and wire locations

Metrics: Skew Power

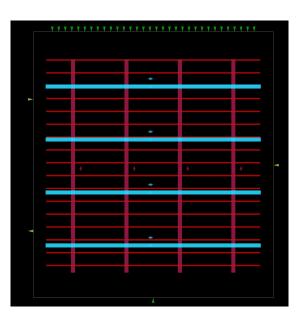

## Routing

Goal: Connect all signals on gates using multiple metal layers

Two stages:

- 1) Global Routing

- 2) Detailed Routing

Metrics: Wire length Congestion Delay Power

| -                                             |  |  | ŧ |  |  |

|-----------------------------------------------|--|--|---|--|--|

|                                               |  |  |   |  |  |

|                                               |  |  |   |  |  |

|                                               |  |  |   |  |  |

| 2 <b>1997 199</b><br>2 1999 199<br>2 1999 199 |  |  |   |  |  |

# Static Timing Analysis (STA)

Goal: Evaluate timing (and power) of circuit

Evaluates minimum and maximum (hold and setup) times of all paths Static means it doesn't consider logic function Ideal or non-ideal clocks Run at each stage of design

Metrics: Delay Slack Dynamic power Leakage power

## **Remaining Steps**

- Parasitics STA

- Engineering Change Order (ECO)

- **Diode Insertion**

- IR Drop

- **GDS** Generation

- Layout vs. Schematic (LVS)

- Design Rule Check (DRC)

- Antenna Check

- Circuit Validity Checks (CVC)

## **Project Discussion**

**Project Consult**

Informal discussion with Jesse and/or I before you write a proposal. Due in 1 week.

Project Proposal 1-2 page proposal. Due in 2 weeks.

## Demo!

**Example TCL Scripts**

Example config.json

Viewing reports and results

Using OpenRoad GUI

#### **Next Lecture**

- Cell libraries

- Next next lecture: Static Timing Analysis