# Lecture 04: Devices and CMOS

Matthew Guthaus Professor UCSC, Computer Science & Engineering <u>http://vlsida.soe.ucsc.edu</u> mrg@ucsc.edu

# Today's Lecture

- Semiconductor Devices

- Diode

- Field Effect Transistor (FET)

- Width, Length and R<sub>on</sub>

- Body Connection

- Parasitic Capacitance and Resistance

- · CMOS Review

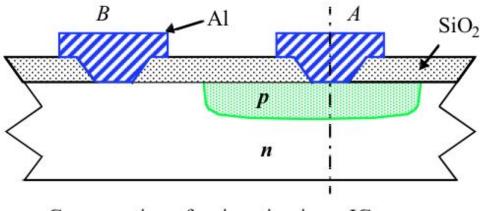

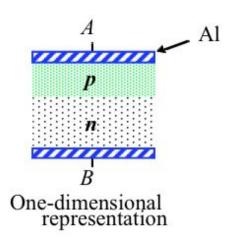

# The Diode

Cross-section of *pn*junction in an IC process

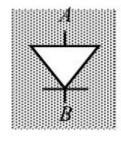

diode symbol

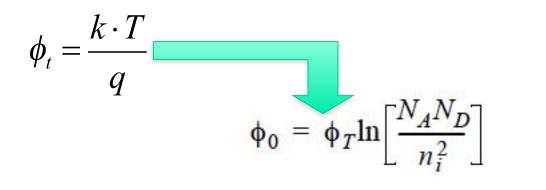

# **Depletion Region**

Drift is charge based Diffusion is concentration based

$N_A$  is concentration of acceptors  $N_D$  is concentration of donors  $n_i$  is "intrinsic concentration"

$$\phi_0 = 26 \ln \left[ \frac{10^{15} \times 10^{16}}{2.25 \times 10^{20}} \right] \text{ mV} = 638 \text{ mV}$$

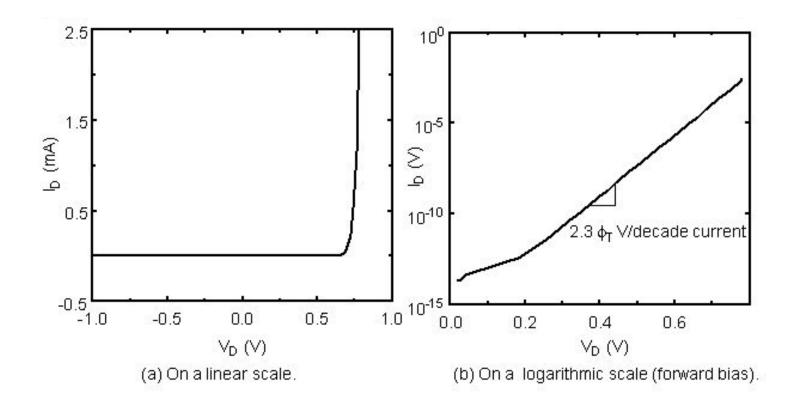

### **Diode Current**

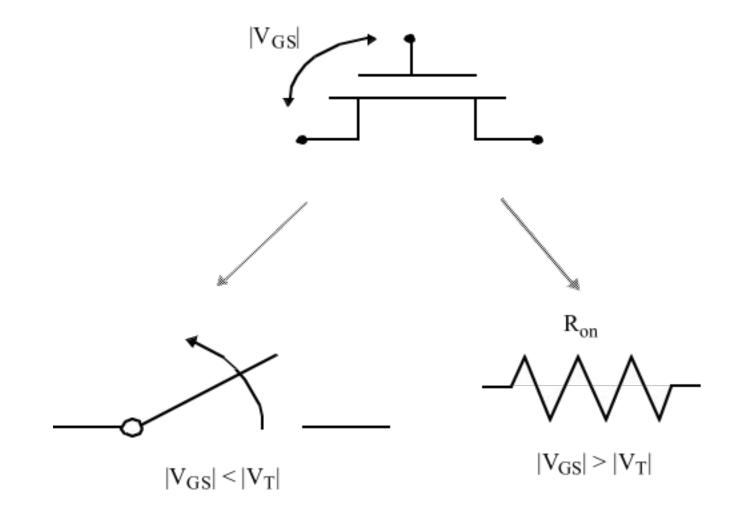

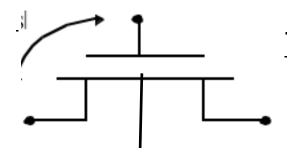

### Switch Model of CMOS Transistor

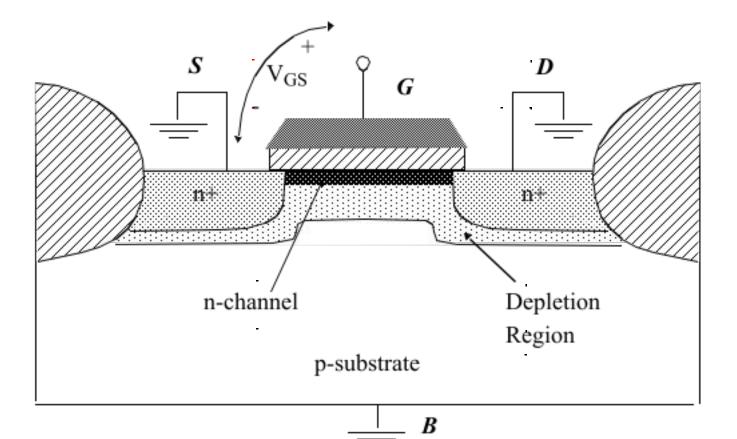

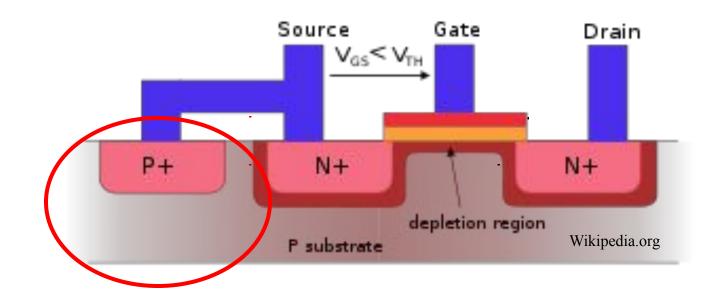

### **Threshold Voltage: Concept**

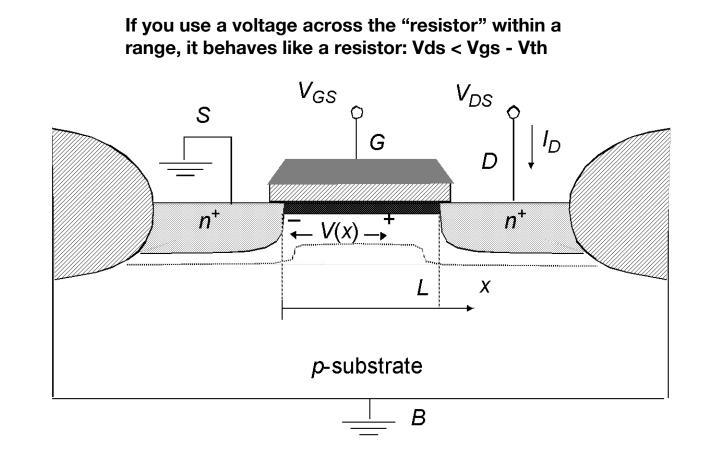

## **Transistor in Linear**

MOS transistor and its bias conditions

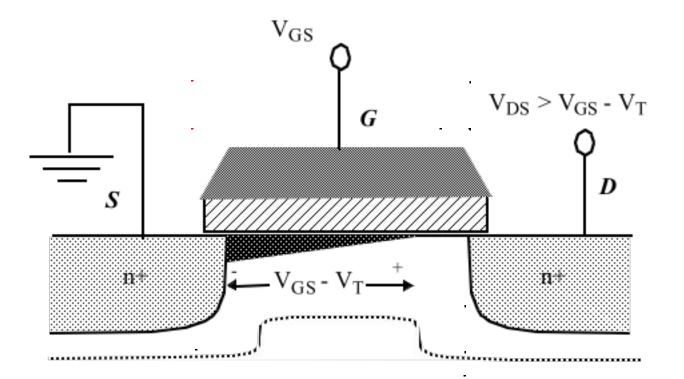

# **Transistor in Saturation**

0

# **Current-Voltage Relations**

Linear Region: V<sub>DS</sub>  $\leq$ V<sub>GS</sub> - V<sub>T</sub>

$$I_{D} = k_{n}^{\prime} \frac{W}{L} \left( (V_{GS} - V_{T}) V_{DS} - \frac{V_{DS}^{2}}{2} \right)$$

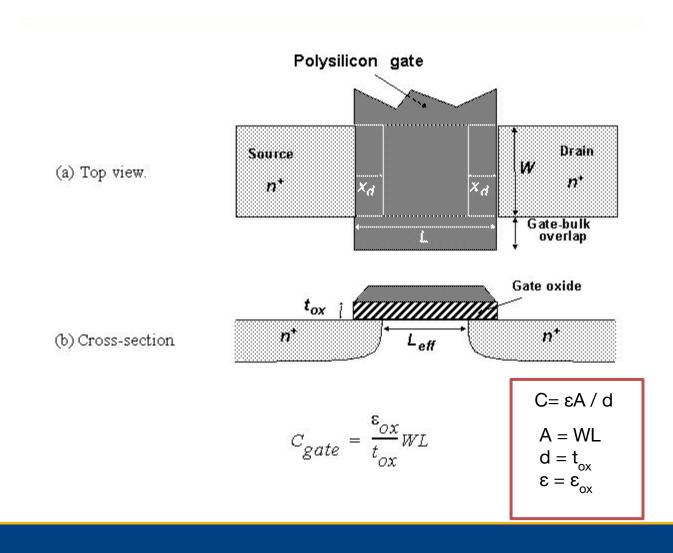

with

$$k'_n = \mu_n C_{ox} = \frac{\mu_n \varepsilon_{ox}}{t_{ox}}$$

Process Transconductance Parameter

Saturation Mode:  $V_{DS} \ge V_{GS} - V_T$  $I_D = \frac{k'_n W}{2 L} (V_{GS} - V_T)^2 (1 + \lambda V_{DS})$ Channel Length Modulation

Mobility of electrons is  $\sim$ 2-3x that of holes.

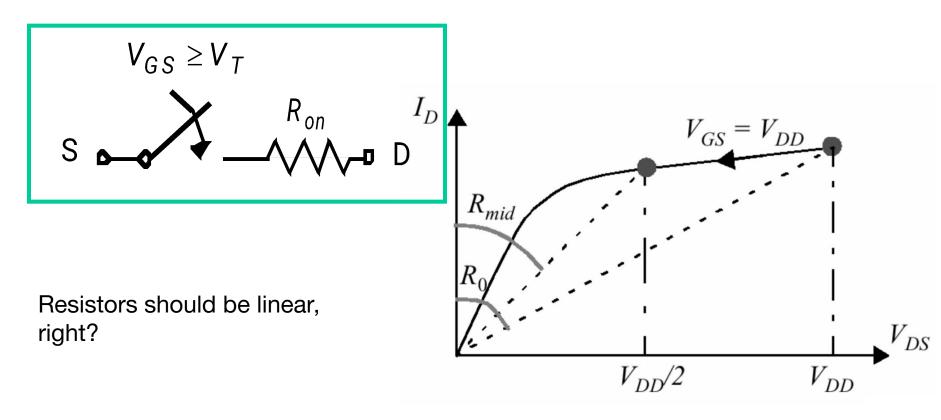

### Transistor as a Switch

R = Vds / Id Ron ≅ average(R0, Rmid)

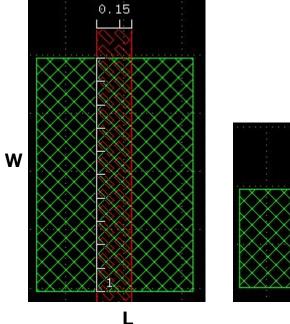

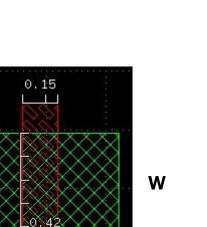

# Width, Length, and Ron

$$I_D = k'_n \frac{W}{L} \left( (V_{GS} - V_T) V_{DS} - \frac{V_{DS}^2}{2} \right)$$

$$I_D = \frac{k'_n}{2} \frac{W}{L} \left( (V_{GS} - V_T)^2 (1 + \lambda V_{DS}) \right)$$

L

Ron  $\infty$  Vds / Id Id  $\infty$  W / L Ron  $\infty$  (Vds \* L) / W

# **Back-Gate Biasing**

If a pwell or nwell (or bulk), can bias the well to adjust threshold.

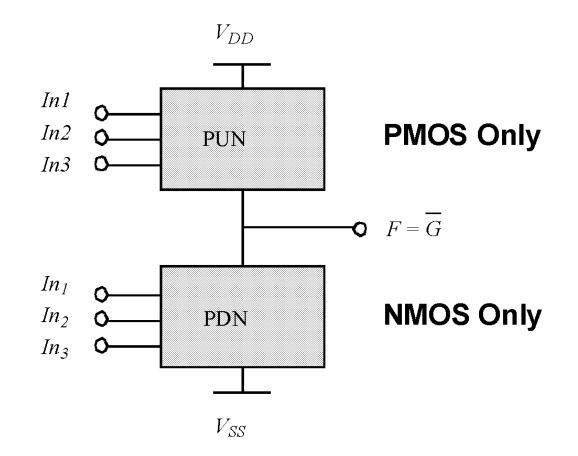

### Static CMOS

#### **PUN and PDN are Dual Networks**

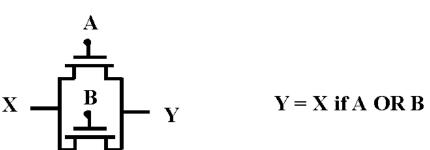

### **NMOS Transistors in Series/Parallel Connection**

Transistors can be thought as a switch controlled by its gate signal NMOS switch closes when switch control input is high

$$\begin{array}{ccc} A & B \\ \blacksquare & \blacksquare \\ X & \blacksquare & \blacksquare \\ \end{array} \qquad Y = X \text{ if A and } B$$

#### NMOS Transistors pass a "strong" 0 but a "weak" 1

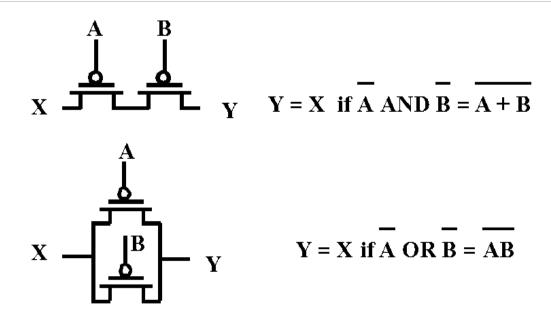

### **PMOS Transistors in Series/Parallel Connection**

PMOS switch closes when switch control input is low

PMOS Transistors pass a "strong" 1 but a "weak" 0

Complementary CMOS Logic Style Construction (cont.)

• PUP is the <u>DUAL</u> of PDN (can be shown using DeMorgan's Theorem's)

$$\overline{\overline{A} + B} = \overline{\overline{A}}\overline{\overline{B}}$$

$$\overline{\overline{A}}\overline{\overline{B}} = \overline{\overline{A}} + \overline{\overline{B}}$$

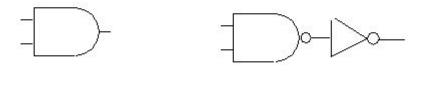

• The complementary gate is inverting

AND = NAND + INV

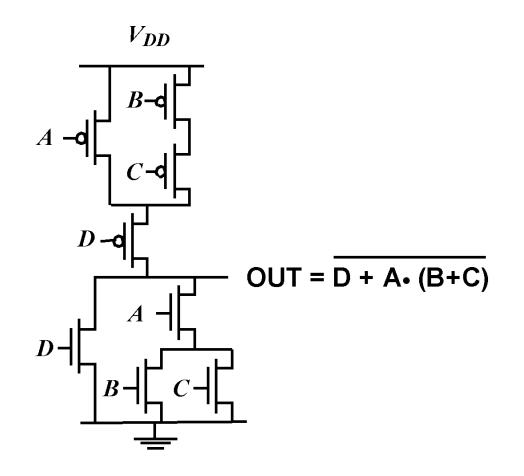

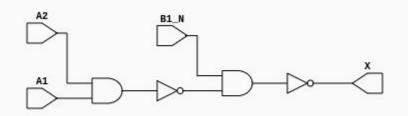

### Example Gate: COMPLEX CMOS GATE

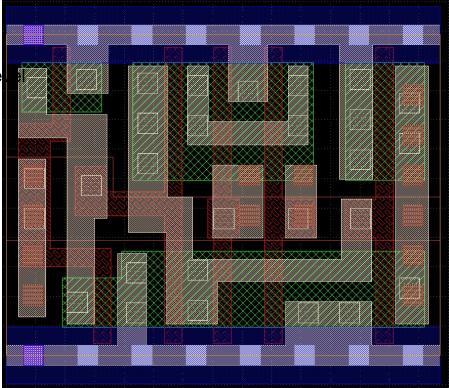

# Example: Sky130 a21bo Gate

(NOTE: This is the logical schematic, not a transistor le schematic!)

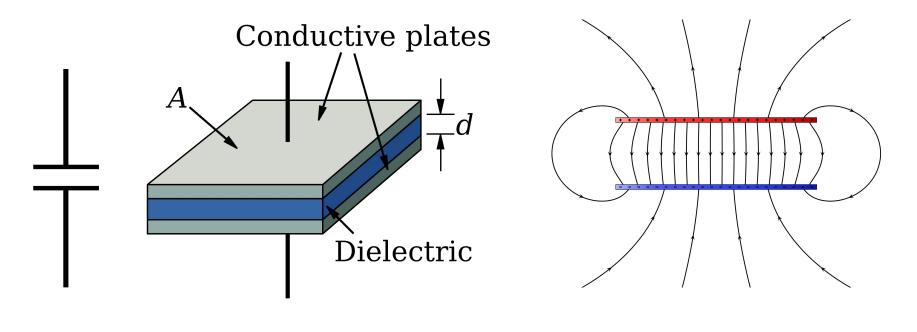

### **Parallel Plate Capacitance**

$C = \epsilon A / d$

### The Gate Capacitance

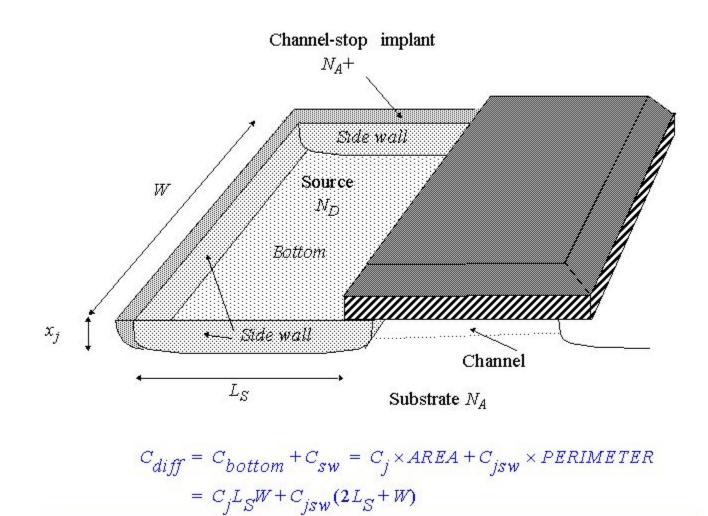

### **Diffusion Capacitance**

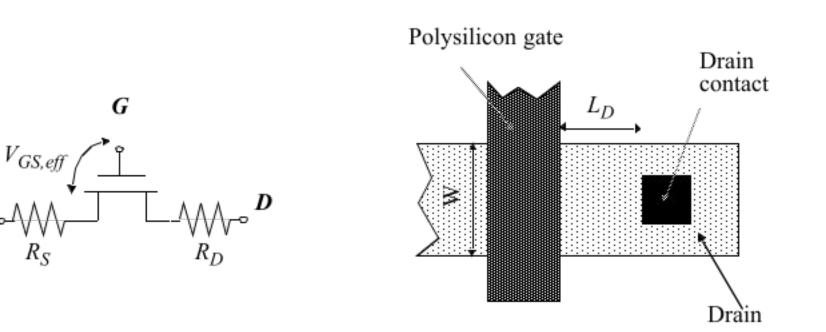

### Parasitic Resistances

S

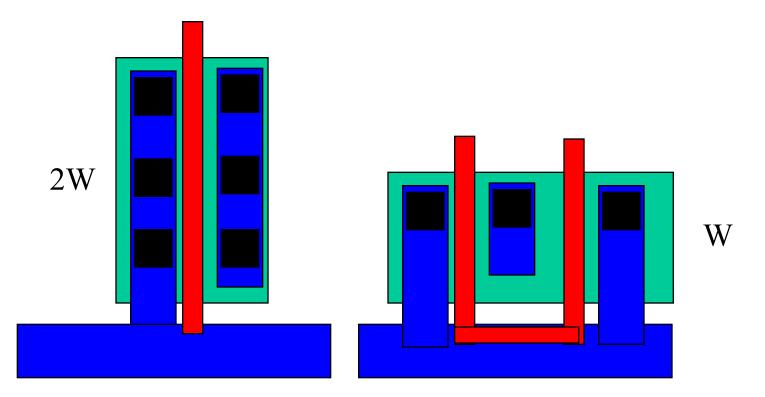

## **Folding Transistors**

### **Next Class**

- Tuesday: Jesse lecture

- Help with klayout

- OpenRAM memory generation

- Review Q&A

- Thursday: Quiz 1