### Lecture 03: Layout

Matthew Guthaus Professor UCSC, Computer Science & Engineering <u>http://vlsida.soe.ucsc.edu</u> mrg@ucsc.edu

#### Today's Lecture

- Layers and Masks

- Design Rules

- Transistor Layout

- Klayout and DRC/LVS demo!

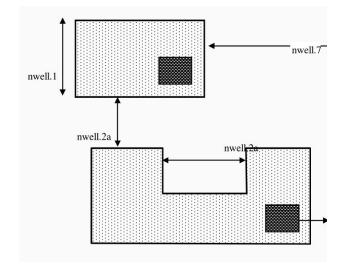

# **Design Rules**

- Interface between the circuit designer and process engineer

- Guidelines for constructing process masks

- Unit dimension: minimum feature size (transistor gate length)

- scalable design rules: lambda parameter

- absolute dimensions: micron rules

- Rules constructed to ensure that design works even when small fab errors (within some tolerance) occur

- A complete set includes

- set of layers

- intra-layer: relations between objects in the same layer

- inter-layer: relations between objects on different layers

# Why Have Design Rules?

To be able to tolerate some level of fabrication errors such as

- 1. Mask misalignment

- 2. Dust

- 3. Process parameters (e.g., lateral diffusion)

- 4. Rough surfaces

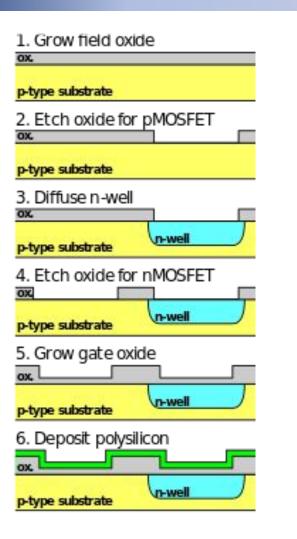

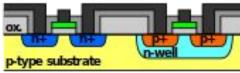

# **Typical CMOS Process**

7. Etch polysilicon and oxide

8. Implant sources and drains

| OX.              |         |

|------------------|---------|

|                  | p+ p+   |

| p-type substrate | (I-Weil |

#### 9. Grow nitride

| ox F             |       |

|------------------|-------|

| p-type substrate | p+ p+ |

#### 10. Etch nitride

#### 11. Deposit metal

#### 12. Etch metal

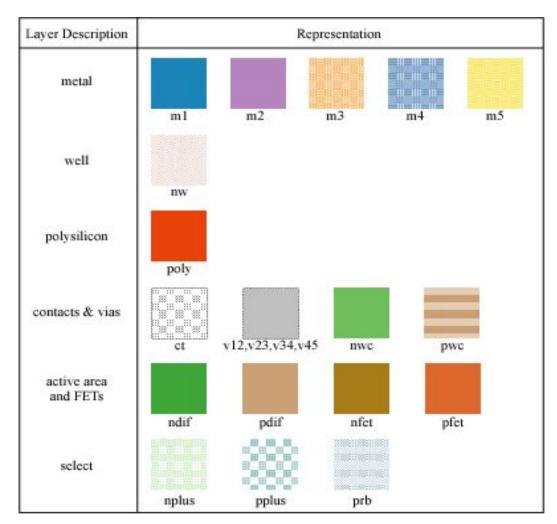

#### **Typical CMOS Process Layers**

| Layer                                          | Key points:                                                                                                                                                                          |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Well (p,n)                                     | N-well process 🛛 p-type wafer (no p-well)                                                                                                                                            |

| Diffusion                                      | Diffusion (Active area) determines where transistors may go                                                                                                                          |

| Polysilicon                                    | Poly overlapping with active = transistor                                                                                                                                            |

| Select (p+,n+)                                 | Select is where n+ and p+ ion implantation<br>occurs; it can be used to place an opposite<br>type region (e.g., put p+ select within n-well to<br>create a p+ well plug, more later) |

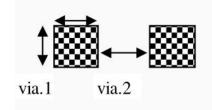

| Contact To Poly<br>Contact To Diffusion<br>Via | All contacts/vias are the same size                                                                                                                                                  |

LI, Metal1, Metal2

# Layers in the book's 0.25 um CMOS process

The book's process is NOT exactly the same as the one we will be using

### Sky130 Layers

prBoundary.boundary - 235/4 pwell.pin - 122/16 pwell.label - 64/59 nwell.drawing - 64/20 nwell.pin - 64/16 nwell.label - 64/5 dnwell.drawing - 64/18 / / diff.drawing - 65/20 tap.drawing - 65/44 psdm.drawing - 94/20 nsdm.drawing - 93/44 poly.drawing - 66/20 poly.pin - 66/16 poly.label - 66/5 poly.model - 66/83 hvtp.drawing - 78/44 9333S licon1.drawing - 66/44 npc.drawing - 95/20 li1.drawing - 67/20 mcon.drawing - 67/44 met1.drawing - 68/20 met1.pin - 68/5 met1.label - 68/16 via.drawing - 68/44 ()met2.drawing - 69/20 met2.pin - 69/16 met2.label - 69/5  $\mathbf{F} + \mathbf{F} + \mathbf{F}$ ncm.drawing - 92/44

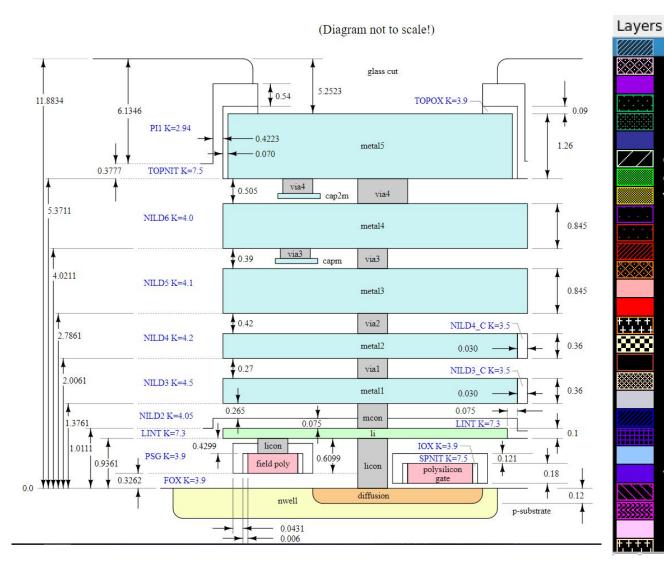

#### A 45nm Process

- NOTE: drw vs net use drawing

- pwell/nwell wells to make tx

- vtg/vth extra implant for high Vth

- active define tx (no field oxide)

- n/p implant makes source/drain

- poly tx gate and routing

- thkox thick oxide for high Vdd tx

- contact hole from metal1 to poly/diff

- metaln/vian metal and via layer n

#### Cadence Virtuoso

| OOOXL              |        |

|--------------------|--------|

| Sort Edit          | Help   |

| pvell              | drw    |

| ICSU_TechLib_Fr    | eePDK4 |

| Layer   Object   G | irid   |

| AV NV AS           | NS     |

| Ĩ                  |        |

| pvell              | drw -  |

| <b>pvell</b>       | net    |

| nvell              | drw    |

| nvell              | net    |

| vtg                | drw    |

| vtg                | net    |

| vth                | drw    |

| wth                | net    |

| active             | drw    |

| active             | net    |

| nimplant           | drw    |

| pimplant           | drw    |

| poly               | drw    |

| poly               | net    |

| poly               | blk    |

| thkox              | drw    |

| Contact            | drw    |

| contact            | net    |

| netal1             | drw    |

| netall             | net    |

| viəl               | drw    |

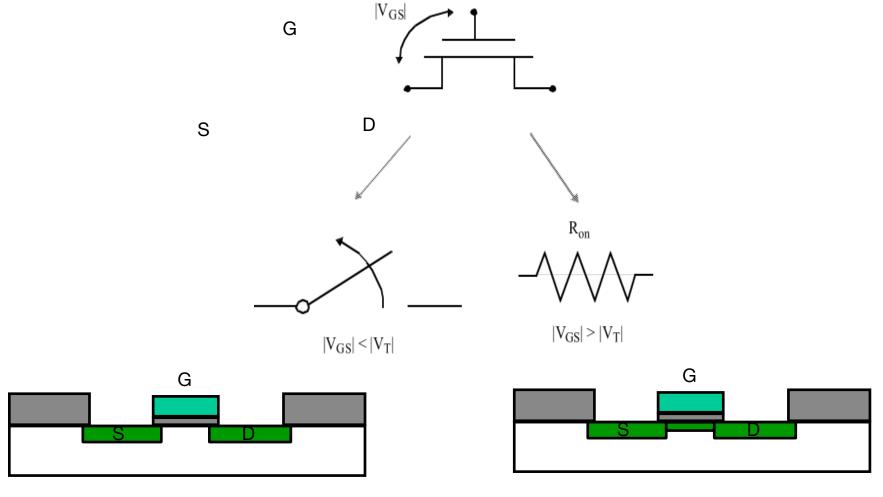

#### **Basic Field-Effect Transistor**

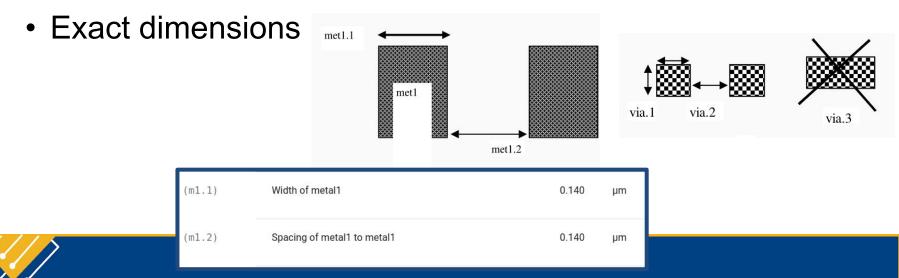

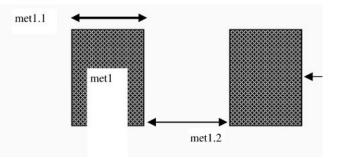

#### Intra-Layer Design Rules

- Minimum dimensions (e.g., widths) of objects on each layer to maintain that object after fab

- minimum line width is set by the resolution of the patterning process (photolithography)

- Minimum spaces between objects (that are not related) on the same layer to ensure they will not short after fab

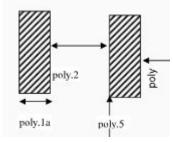

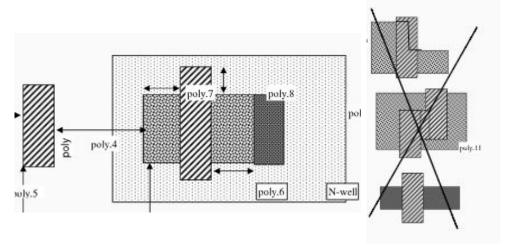

#### (Some) Intra-Layer Rules

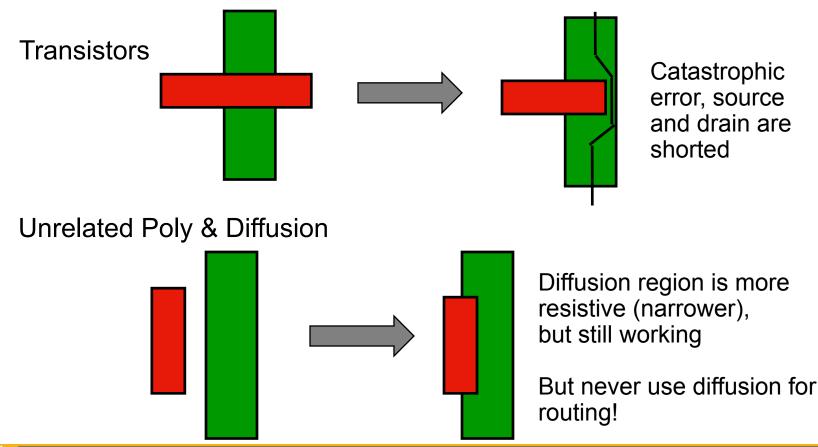

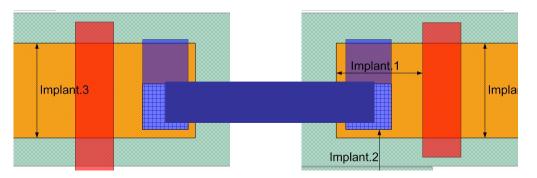

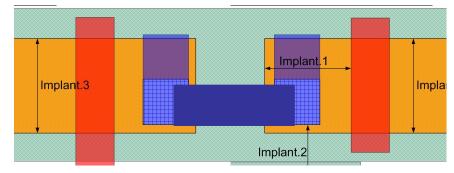

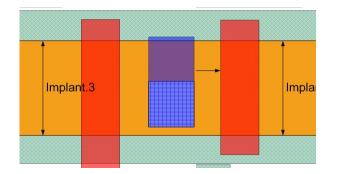

#### Inter-Layer Design Rules

Transistor rules – transistor formed by overlap of diffusion (also called active) and poly layers

#### (Some) Inter-Layer Rules

(m1.4)

(m1.4a)

(m1.5)

| (poly.4) | Spacing of poly on field to diff (parallel edges only) | Р | 0.075 | μm |

|----------|--------------------------------------------------------|---|-------|----|

| poly.5)  | Spacing of poly on field to tap                        | Р | 0.055 | μm |

| (poly.6) | Spacing of poly on diff to abutting tap (min source)   | Ρ | 0.300 | μm |

| (poly.7) | Extension of diff beyond poly (min drain)              | Р | 0.250 |    |

| mcon   |        |

|--------|--------|

| +      | met1.5 |

|        |        |

| met1.4 |        |

|   | Mcon must be enclosed by Met1 by at least<br>(Rule exempted for cell names documented in rule m1.4a)                                                                                                                | Ρ    | 0.030 | μm |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|----|

| ) | Mcon must be enclosed by Met1 by at least (for<br>cell names "s8cell_ee_plus_sseln_a",<br>"s8cell_ee_plus_sseln_b",<br>"s8cell_ee_plus_sselp_a",<br>"s8cell_ee_plus_sselp_b", "s8fpls_pl8", and<br>"s8fs_cmux4_fm") | Ρ    | 0.005 | μm |

|   | Mcon must be enclosed by Met1 on one of two adjacent sides by at least                                                                                                                                              | P AL | 0.060 | μm |

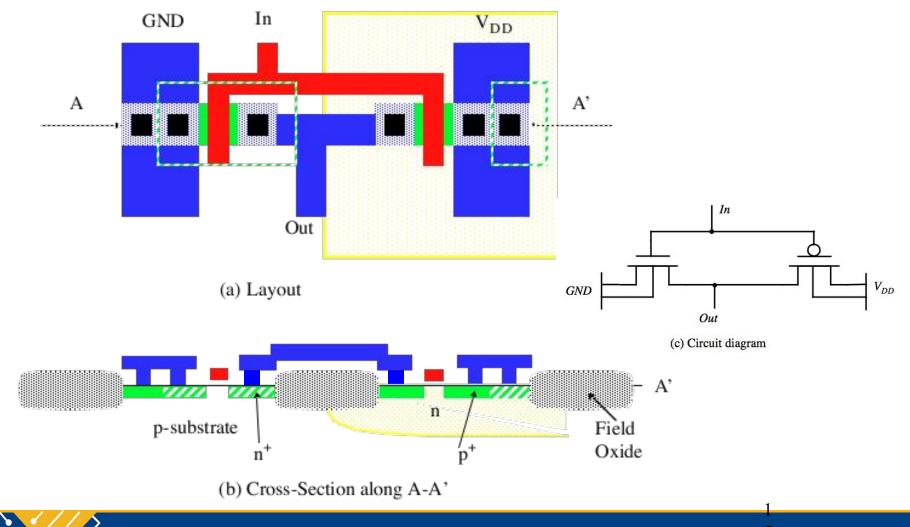

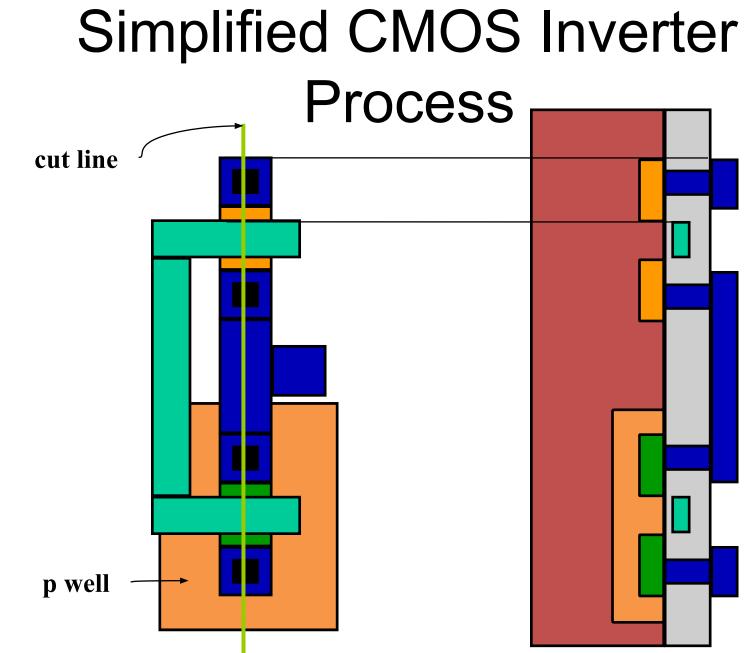

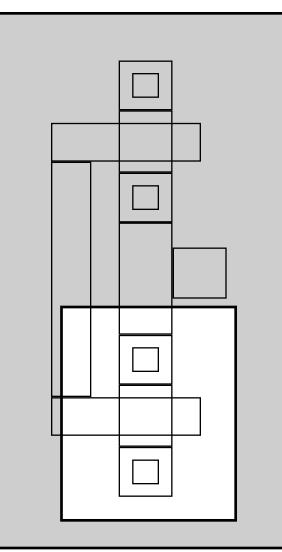

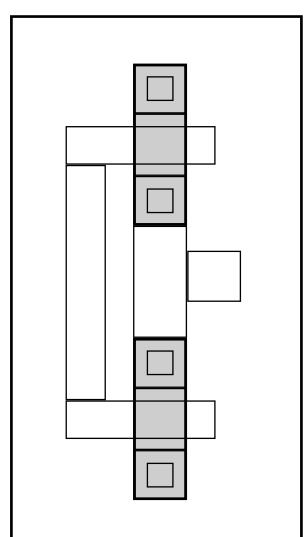

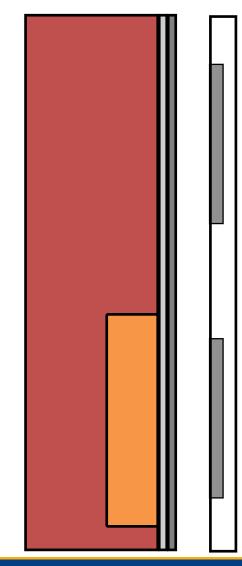

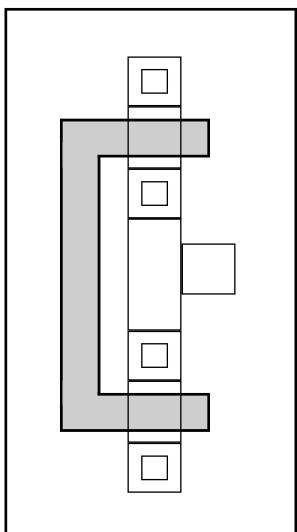

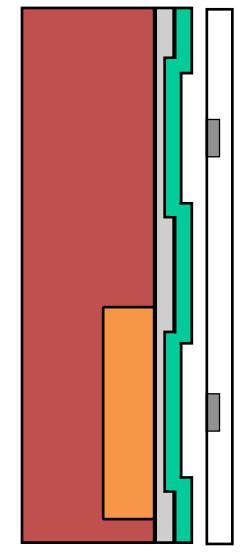

#### **CMOS Inverter Layout**

А

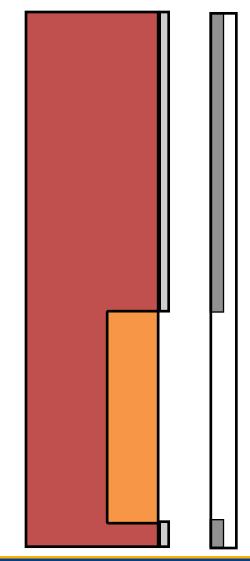

# P-Well Mask (pwell or nwell)

### Active Mask (diff)

### Poly Mask (poly)

#### P+ Select Mask (psdm)

#### N+ Select Mask (nsdm)

# Contact Mask (licon+npc)

### Metal Mask(m1)

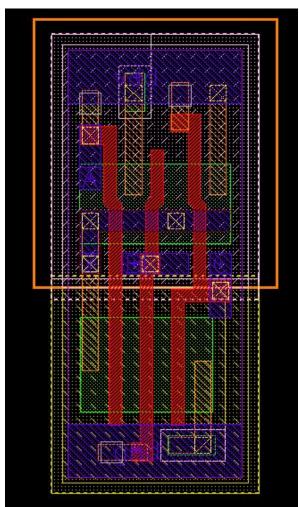

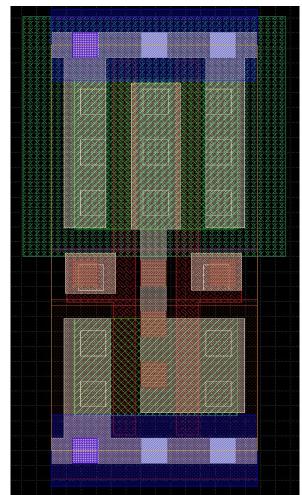

#### Example Layout: INV1

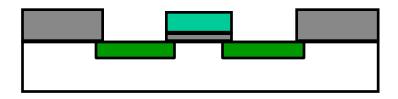

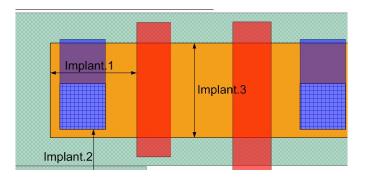

- Horizontal n-diffusion and p-diffusion strips

- Vertical polysilicon gates

- Metal1  $V_{DD}$  rail at top

- Metal1 GND rail at bottom

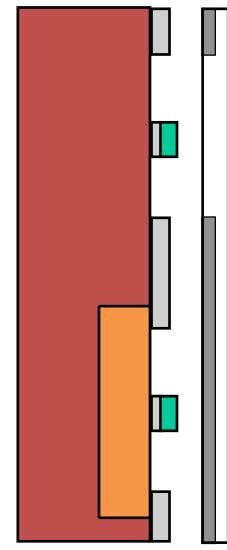

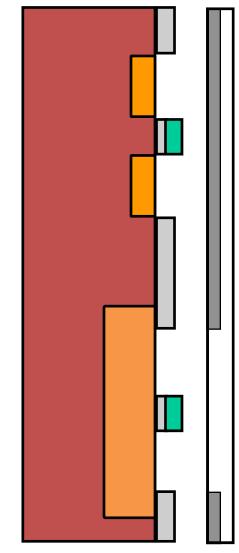

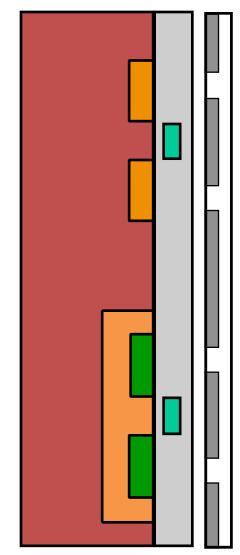

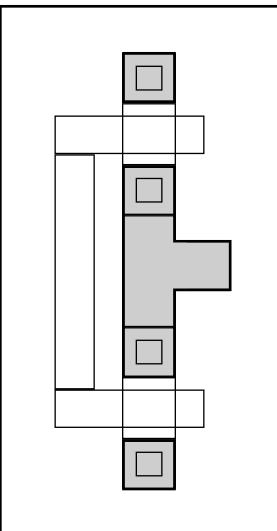

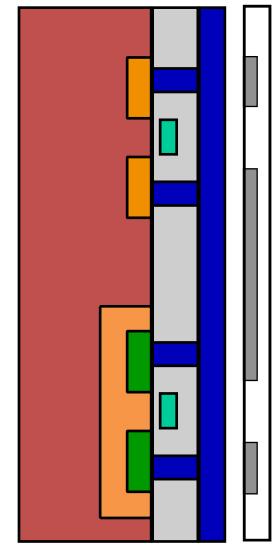

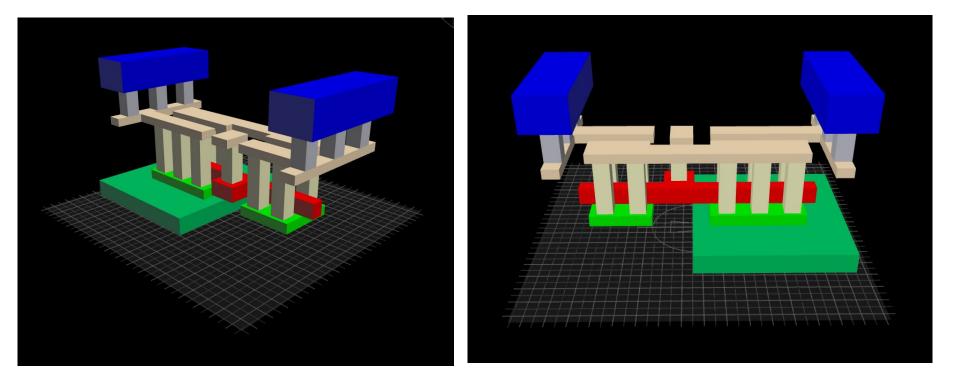

#### 2.5D Views

#### Well and Diffusion Sharing

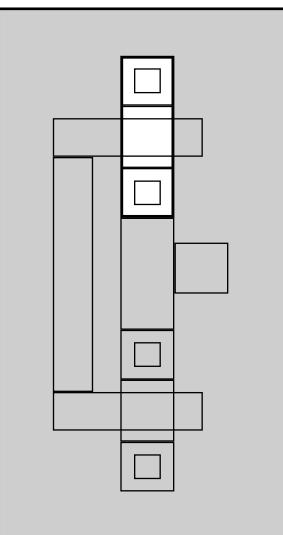

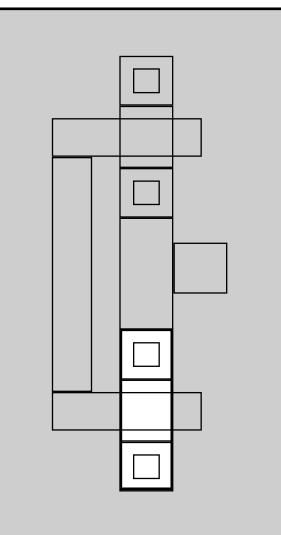

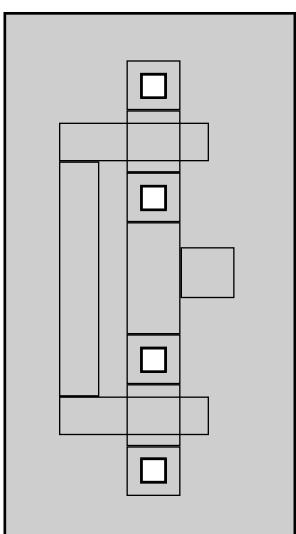

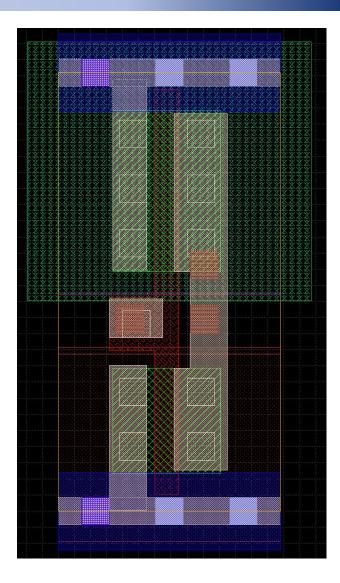

#### Standard Cell - Example

3-input NAND cell (from ST Microelectronics):

2-input NAND cell (from Skywater 130nm):

27

#### Next Lecture

Devices and CMOS