#### Lecture 02: Fabrication

Matthew Guthaus Professor UCSC, Computer Science & Engineering <u>http://vlsida.soe.ucsc.edu</u> mrg@ucsc.edu

#### Syllabus

<u>https://vlsida.github.io/cse122-222a-s23/s</u>

<u>yllabus.html</u>

#### This is a project class!

### Today's Lecture

- Semiconductor Material types

- Packaging and Dies

- Basic steps of semiconductor processing

- Photolithography

- Oxidation/Etching/Implantation/Deposition

- Planarization

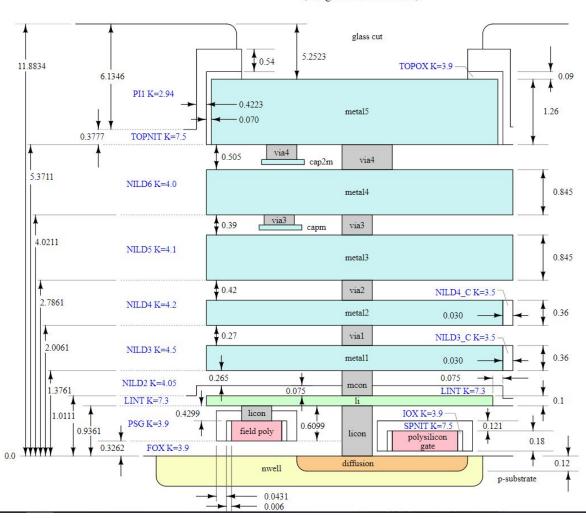

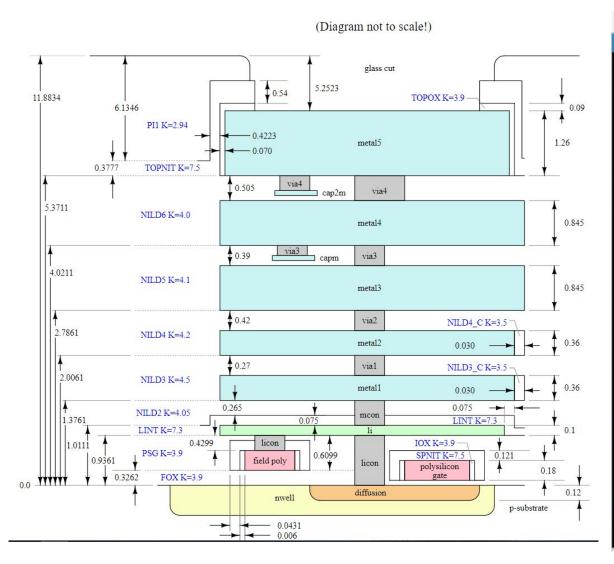

#### Skywater 130nm

(Diagram not to scale!)

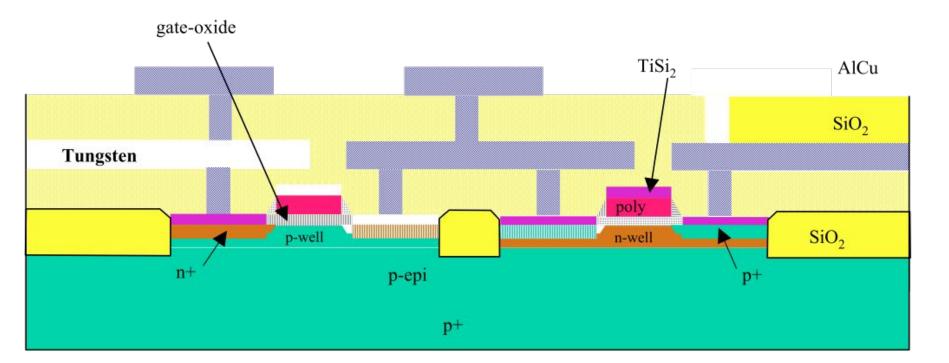

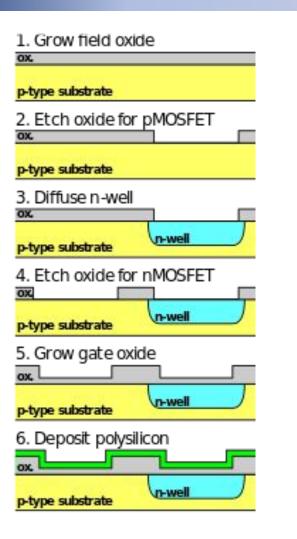

#### A "Modern" CMOS Process

#### **Dual-Well Trench-Isolated CMOS Process**

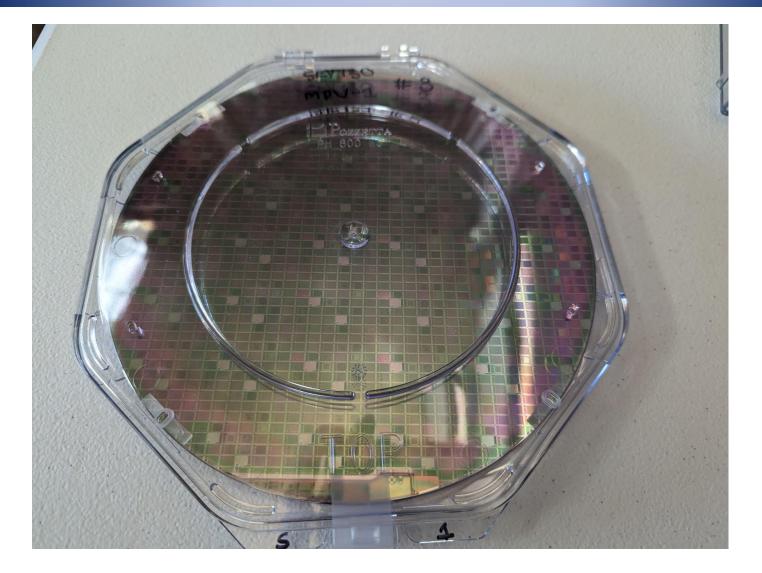

#### The Wafer

- 450mm wafer size (18 in)

- P-type Silicon

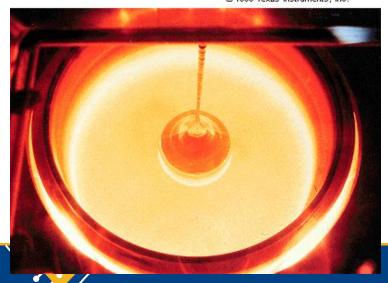

From Computer Desktop Encyclopedia Reproduced with permission. (3) 1996 Texas Instruments, Inc.

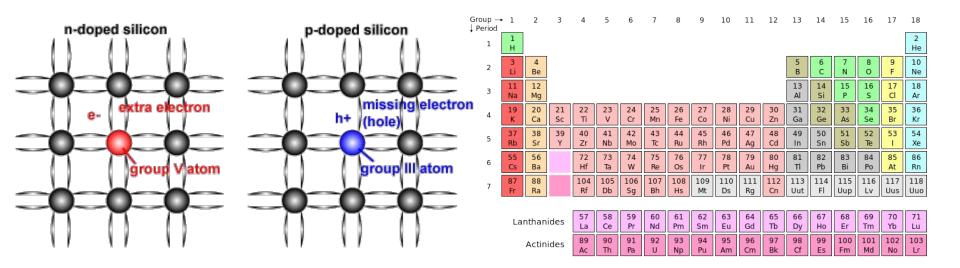

#### N and P-type Silicon

- Silicon has 4 electrons in outer shell

- · N-type has "extra" electrons

- E.g. Phosphorous, group V atom

- · P-type has "extra" holes

- E.g. Boron, group III atom

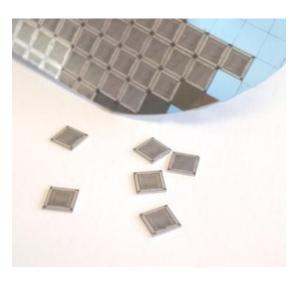

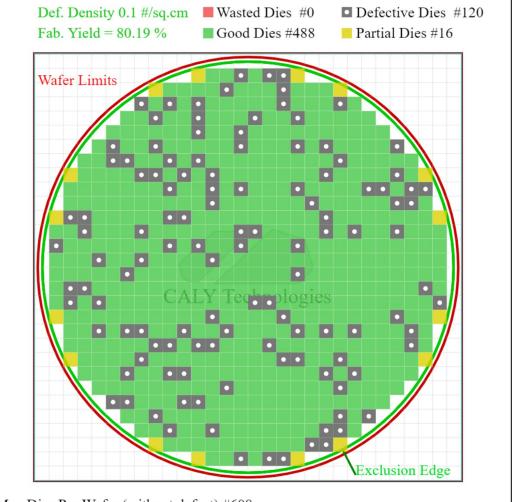

# Wafer Yield

- 15mm x 15mm 18in wafer Loss

- Scribe lines

- Edges

- Defects

Max Dies Per Wafer (without defect) #608

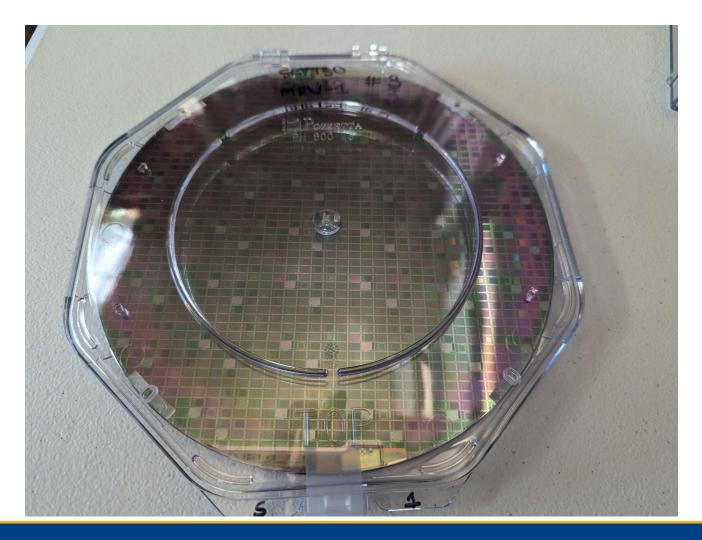

#### Skywater 130nm Wafer

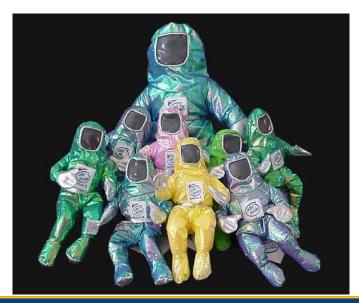

### **Clean Rooms**

- Class 100, 1000, ...

- 0.5um per ft^3

- Often "hoods" for very clean areas

- Particles cause defects...

- Bunny suits

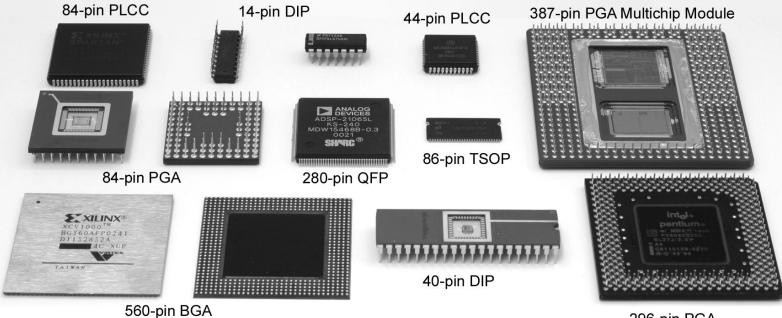

#### Package Types

296-pin PGA

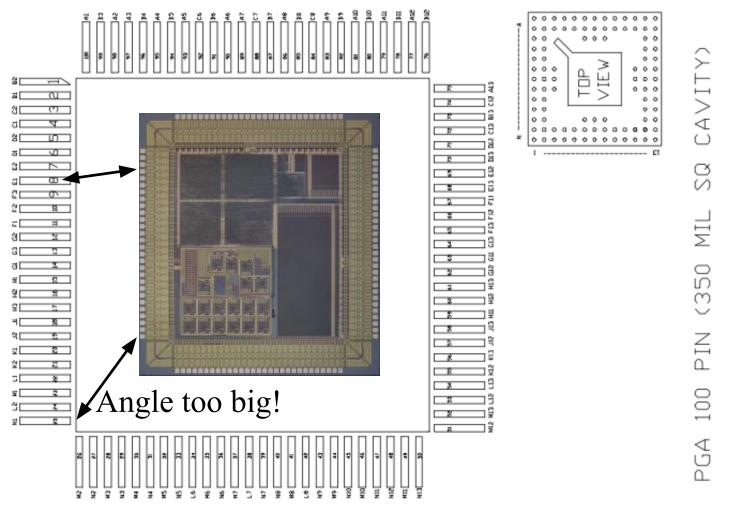

## Pin Grid Array (PGA) Package

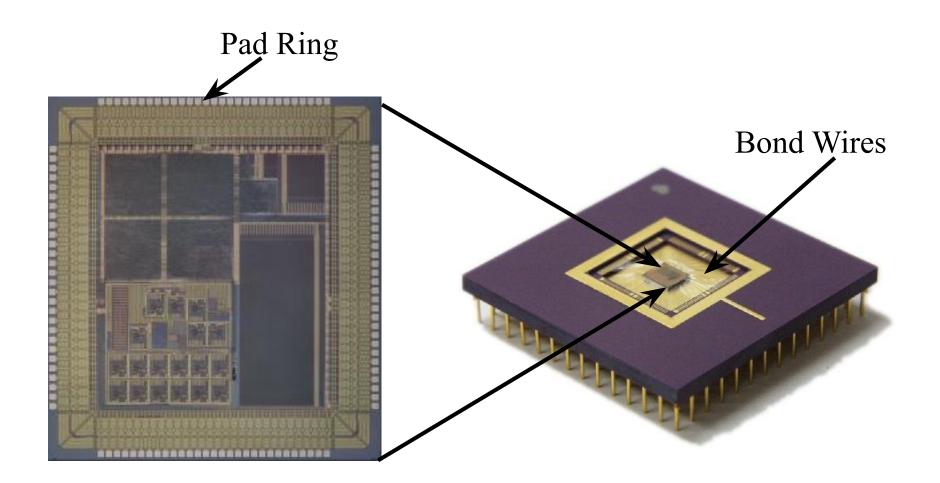

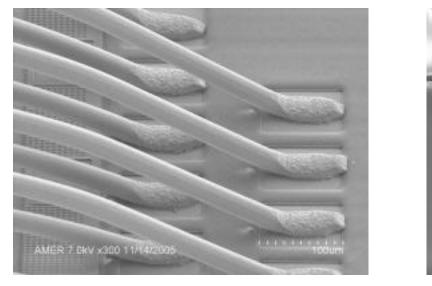

### **Bond Wires**

Connect pads to chip with Au or Al wires Wedge Bond

Ball Bond

90%

10%

From klabs.org

### PGA 100 Bond Diagram

Limit on bond wire length too.

1 mil = 25.4 microns

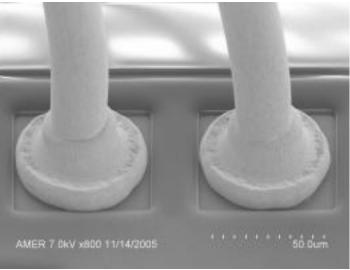

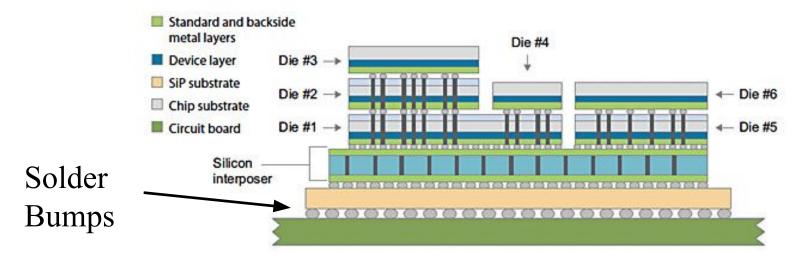

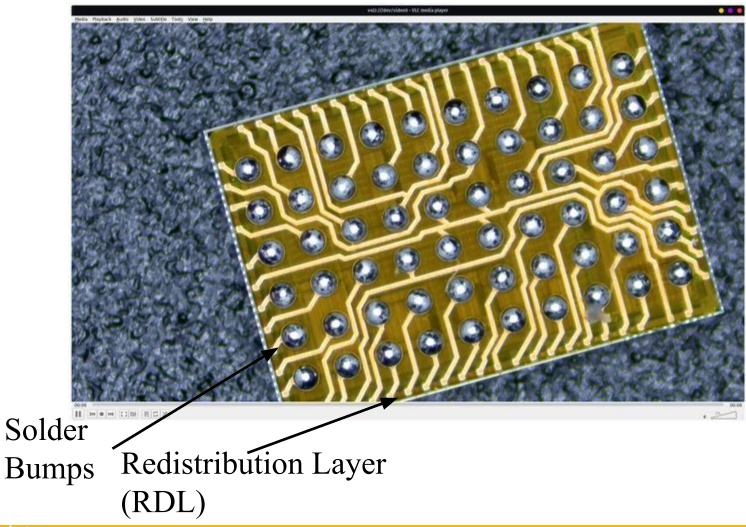

# Flip Chip

- Flip-chip places connections across surface of die rather than around periphery (allows 300-400 IO)

- Top level metal pads covered with solder balls

- Chip flips upside down

- Carefully aligned to package (done blind!)

- Heated to melt balls

- Also called C4 (Controlled Collapse Chip Connection)

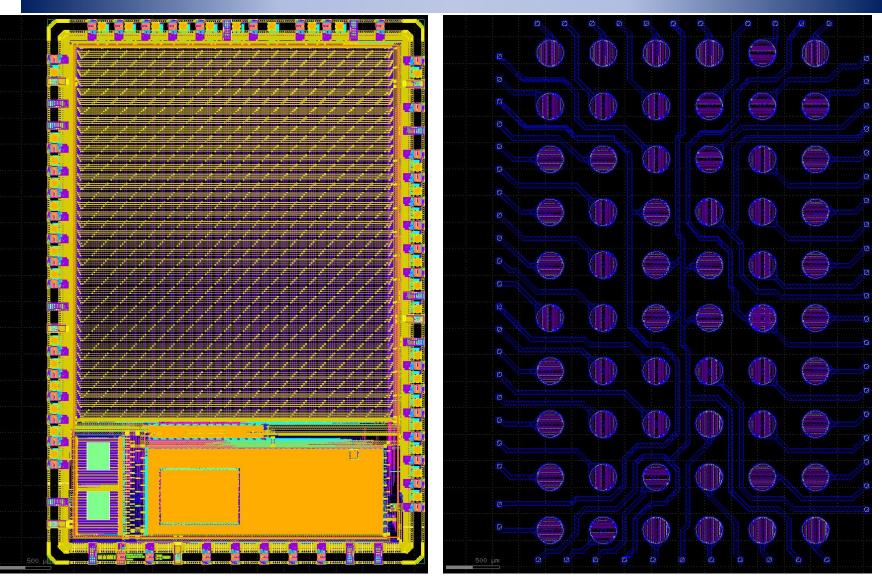

### **OpenRAM MPW2 Test Chip**

#### **Bump Bond Overlap Mask**

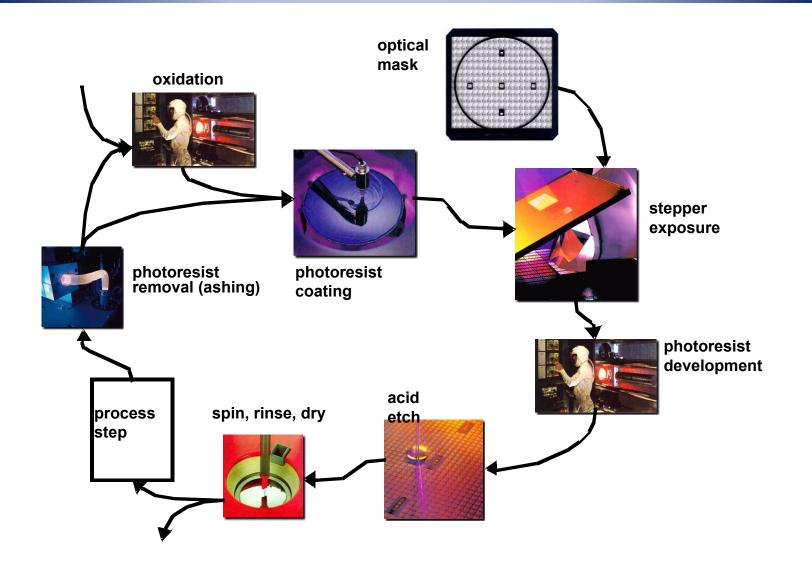

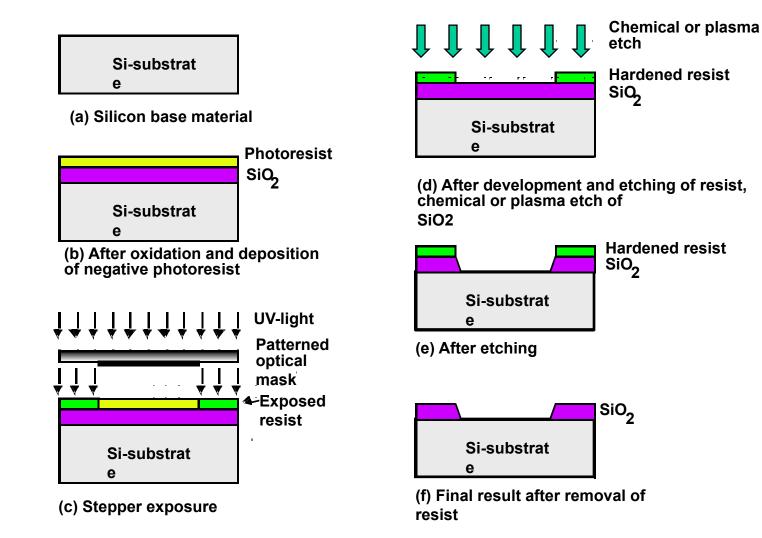

## **Photolithographic Process**

Typical operations in a single photolithographic cycle (from [Fullman]).

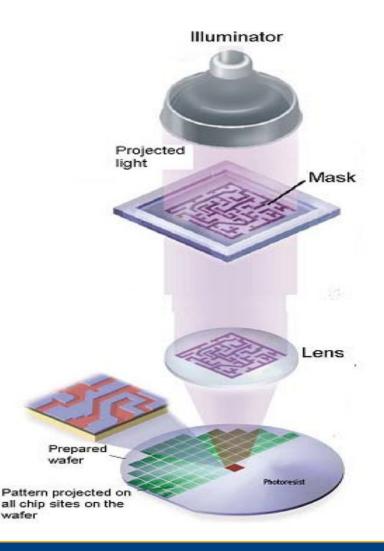

# Photolithography

- UV is 192nm, but our dimensions are less than this

- Samsung/TSMC EUV (13.5nm) for 5nm

## Sky130 MPW-1 Metal 1 Mask

#### Skywater 130nm Wafer

#### ~8 inch wafer (200mm)

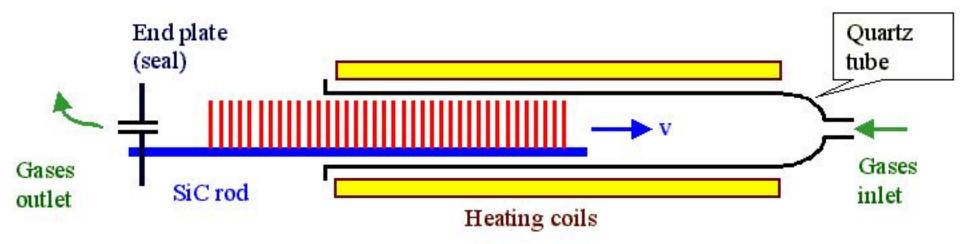

## Oxidation

- Mix oxygen and hydrogen

- 1000C

- Turns Si to SiO2

- Slower growth yields finer/better oxide (e.g. gate)

# Patterning of SiO<sub>2</sub>

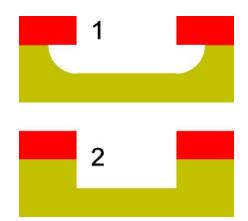

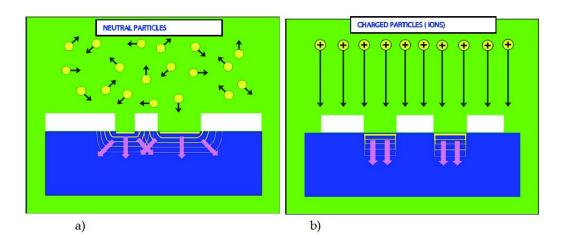

# Etching

- Used to form patterns

- Wet Etching

- Acid or base solution

- Isotropic (all directions) etch

- Dry (Plasma) Etching

- Negative charge wafer, 100C, vacuum

- Fill with positive plasma (Nitrogen, Chlorine, Boron trichloride)

- Anisotropic "sandblasting" in one direction

# Implantation

- Change dopant concentration

- P-type or n-type or p+-type or n+-type

- Diffusion (slow)

- High temp 900-1100C

- Greatest concentration at surface

- Ion (fast)

- Shoots beam at surface

- Depth depends on speed

- Must anneal the material to fix damage

# Deposition

- Chemical Vapor Deposition (CVD)

- Silicon Nitride (Si3N4)

- Gas-phase reaction at 850C

- Polysilicon

- Sputtering

- Aluminum

- Physical Vapor Deposition (PVD)

Copper

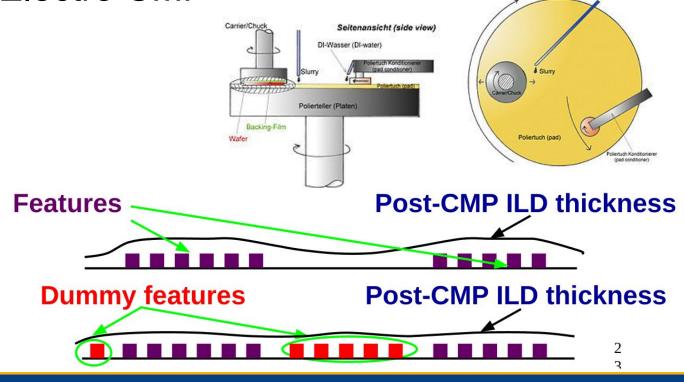

### Planarization

- Chemical Mechanical Polishing (CMP)

- Slurry liquid with abrasive like silica

- Flexible pad grinds a layer off

- Electro CMP

Draufsicht (top view)

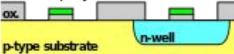

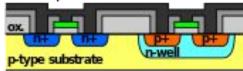

# **Typical CMOS Process**

7. Etch polysilicon and oxide

8. Implant sources and drains

| OX.              |         |

|------------------|---------|

|                  | p+ p+   |

| p-type substrate | Vieweii |

#### 9. Grow nitride

| ox 🗖             |        |

|------------------|--------|

|                  | p+ p+  |

| p-type substrate | Triven |

#### 10. Etch nitride

#### 11. Deposit metal

#### 12. Etch metal

# Sky130 Layers

Layers prBoundary.boundary - 235/4 pwell.pin - 122/16 pwell.label - 64/59 nwell.drawing - 64/20 nwell.pin - 64/16 nwell.label - 64/5 dnwell.drawing - 64/18 diff.drawing - 65/20 tap.drawing - 65/44 psdm.drawing - 94/20 nsdm.drawing - 93/44 poly.drawing - 66/20 poly.pin - 66/16 poly.label - 66/5 poly.model - 6<u>6/83</u> hvtp.drawing - 78/44 2225 licon1.drawing - 66/44 npc.drawing - 95/20 li1.drawing - 67/20 mcon.drawing - 67/44 met1.drawing - 68/20 met1.pin - 68/5 met1.label - 68/16 via.drawing - 68/44 ())met2.drawing - 69/20 met2.pin - 69/16 met2.label - 69/5 1111 ncm.drawing - 92/44

## Sky130 Layers vs Masks

| La | M  | ρ | r  | ς. |

|----|----|---|----|----|

| LO | x. | ~ | ۰. | ч. |

#### prBoundary.boundary - 235/4

pwell.label - 64/59 nwell.drawing - 64/20 nwell.pin - 64/16 nwell.label - 64/5 dnwell.drawing - 64/18 diff.drawing - 65/20 tap.drawing - 65/44 psdm.drawing - 94/20 nsdm.drawing - 93/44 poly.drawing - 66/20 8889 poly.pin - 66/16 poly.label - 66/5 poly.model - 66/83 hvtp.drawing - 78/44 licon1.drawing - 66/44 npc.drawing - 95/20 li1.drawing - 67/20 mcon.drawing - 67/44 met1.drawing - 68/20 met1.pin - 68/5 met1.label - 68/16 via.drawing - 68/44 met2.drawing - 69/20 met2.pin - 69/16 met2.label - 69/5 1 + + + + ncm.drawing - 92/44

| Table 1 T             | able - Masks |                   | Metal 1                | MM1     | x |

|-----------------------|--------------|-------------------|------------------------|---------|---|

| Mask                  | Acronym      | Used in<br>SKY130 | Via                    | VIM     | x |

| Field Oxide           | FOM          | x                 | Capacitor MiM          | САРМ    |   |

| Deep N-Well           | DNM          | x                 | Metal 2                | MM2     | x |

| P-Well Block Mask     | PWBM         |                   | Via 2-TNV              | VIM2    |   |

| P-Well Drain Extended | PWDEM        |                   | Via 2-S8TM             | VIM2    |   |

| N-Well*               | NWM          | x                 | Via 2-PLM              | VIM2    | x |

| High Vt PCh*          | HVTPM        | х                 | Metal 3-TLM            | ММЗ     |   |

| Low Vt Nch*           | LVTNM        | x                 | Metal 3-S8TM           | MM3     |   |

| HLow VT PCh Radio*    | HVTRM        | х                 | Metal 3-PLM            | MM3     | х |

| N-Core Implant        | NCM          |                   | Pad Via                | VIPDM   |   |

| Tunnel Mask           | TUNM         | х                 | Via3-PLM               | VIM3    | x |

| ONO Mask              | олом         | х                 | Inductor-TLM           | INDM    |   |

| Low Voltage Oxide     | LVOM         | x                 | Metal 4                | MM4     | х |

| Resistor Protect      | RPM          | x                 | Via4                   | VIM4    | х |

| Poly 1                | P1M          | x                 | Metal 5                | MM5     | х |

| N-tip Implant         | NTM          | x                 | Nitride Seal Mask      | NSM     | х |

| High Volt. N-tip      | HVNTM        | x                 | Pad (scribe protect)   | PDM     | х |

| Lightly Doped N-tip   | LDNTM        | x                 | Pad (scribe unprotect) | PDM     |   |

| Nitride Poly Cut      | NPCM         | x                 | Polyimide              | РММ     |   |

| P+ Implant            | PSDM         | x                 | Polyimide_ExtFab       | PMM[E]  |   |

| N+ Implant            | NSDM         | x                 | Pad&Polyimide_ExtFab   | PDMM[E] |   |

| Local Intr Cont.1     | LICM1        | x                 | DECA PBO               | PBO     | х |

| Local Intrenet 1      | LIIM         | x                 | Cu Inductor/Redist.    | CU1M    | Х |

|                       |              |                   | Polyimide 2 (2)        | PMM2    | х |

|                       | CTM1         | х                 | Under Bump Metal       | UBM     |   |

| Open Frame Mask       | OFM          |                   | Bumps                  | BUMP    |   |

#### Next Time

Layout (for HW1!)